【摘要】:图8-1 定时器/计数器实现的答辩倒计时电路2.电路原理系统上电后,各独立按键口线的低电平被U1顺序检测并计次,产生数字0~9可循环键入的10min位和min位预置值,经P1口低4位送至U2和U3进行7段译码,由P1.4口和P1.5口的高电平分别锁存10min位和min位作静态显示。

1.硬件组成

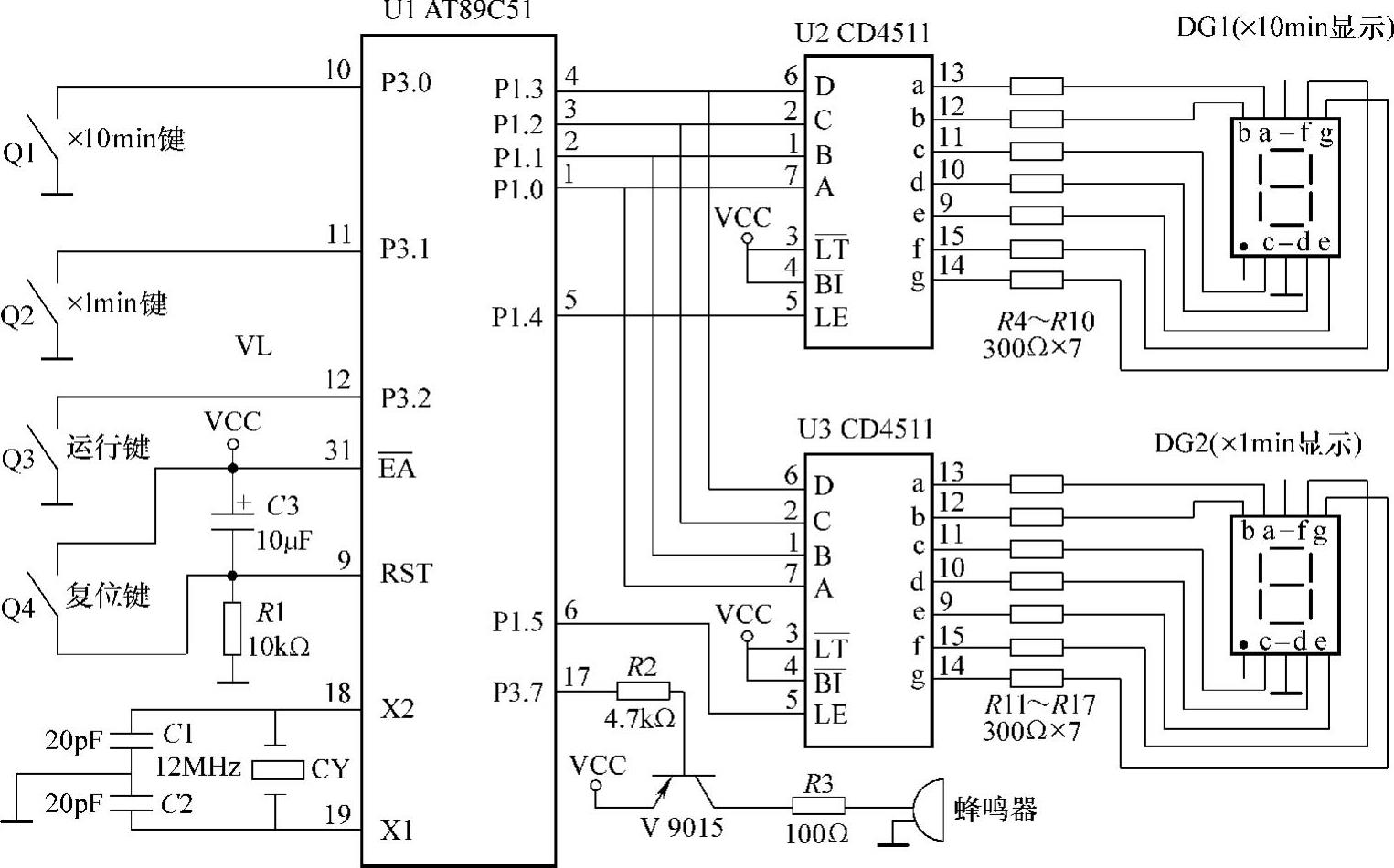

定时器/计数器实现的答辩倒计时电路见图8-1。以单片机芯片U1为控制核心,两位“7段LED共阴极数码管”DG1和DG2作10min位和min位的静态显示,由“7段锁存/译码/驱动芯片”U2和U3作段控制,预置值由两个独立按键Q1和Q2输入,独立按键Q3和Q4分别担任倒计时启动和系统复位,用晶体管V驱动蜂鸣器产生提示音。

图8-1 定时器/计数器实现的答辩倒计时电路

2.电路原理(https://www.xing528.com)

系统上电后,各独立按键口线的低电平被U1顺序检测并计次,产生数字0~9可循环键入的10min位和min位预置值,经P1口低4位送至U2和U3进行7段译码,由P1.4口和P1.5口的高电平分别锁存10min位和min位作静态显示。运行键启动后,由U1内部定时器中断进行计时,每累计到1min则预置值递减1,从P1口低4位送出的数据使显示更新一次,其中min位以秒速率闪动显示,直到两显示位DG1和DG2全为零,此时P3.7送出低电平,晶体管导通便驱动蜂鸣器发声,倒计时结束。

3.主要器件

U1为AT89C51(40脚DIP封装),U2和U3为CD4511,DG1和DG2为超高亮数码管GF5101AS,V为PNP型晶体管9015,蜂鸣器为自振型TMB12A05,Q1~Q4为常开触点按键开关。定时器/计数器实现的答辩倒计时电路装置见图8-2。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。