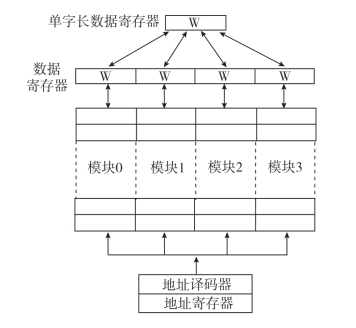

1.单体多字存储器

要想提高存储器的数据传输速率,在同样器件的条件下,只有设法提高存储器的字长。单体是指只有一套地址寄存器和地址译码器,多字是指有多个容量相同的存储模块(例如有N个存储模块)。在一个读/写周期中N个存储模块M0~MN-1同时工作,对N个存储模块中地址相同的单元进行读写。若每个存储模块每次读出W位,那么N个存储模块就可同时读出N×M位。这N个字可同时或分时送往CPU,CPU感觉到存储器的速度提高了N倍。这就是单体多字存储器,图3-13就是单体四字的存储器示意图。

图3-13 单体四字结构存储器

单体多字存储器的优点是实现简单,缺点是访问冲突概率大。当单体多字并行存储器一次取出多个指令字时,就能很好地支持程序的顺序执行。但是,当一个存储字中有一条转移指令字时,那么存储字中转移指令后面被同时预取的几个指令字只能作废。在读操作数时,单体多字并行存储器一次取出的多个数据字不一定都是要执行的指令所需要的操作数,而当前执行指令需要的全部操作数也可能不包含在一个存储字中,因而不能被一次取出。在写数据时,单体多字并行存储器必须是凑齐了多个数据字之后才能作为一个存储字一次写入存储器。因此,需要先把属于一个存储字的多个数读到数据寄存器中,然后再把整个存储字写回存储器。所以,单体多字存储器存在着比较大的局限性。

2.多模块(多体单字)交叉存储器

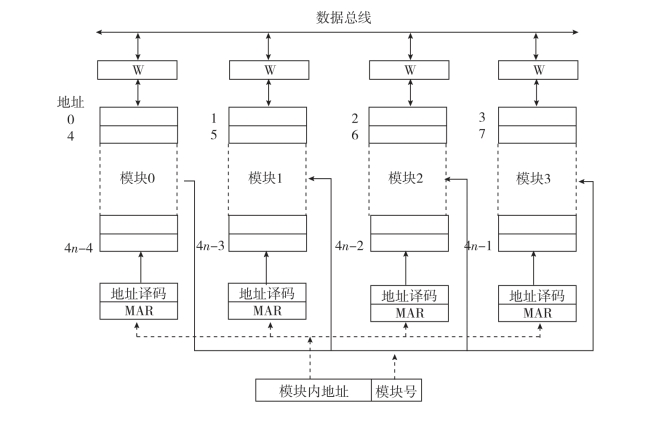

由多个存储模块组成一个更大容量的主存时,对多个存储体的存储单元采用交叉编址方式,组成多模块交叉存储器。多模块交叉存储器通常有两种交叉编址方式,一是地址码的高位交叉编址,二是地址码的低位交叉编址。高位交叉编址存储器目前使用很普遍,这种编址方式能很方便地扩展常规主存的容量,但只有低位地址码交叉编址存储器才能作为并行存储器的一种。地址码的低位字段经过译码选择不同的模块,而高位字段地址码指向相应模块内的存储字。

低位交叉编址存储器是将连续地址分布在相邻的不同模块内,同一个模块内的存储单元地址都是不连续的。每个模块有相同的容量和存取速度,各模块都有独立的地址寄存器、地址译码器、驱动电路和读写电路,它们既能并行工作,又能交叉工作。

所谓的并行工作,即同时访问多个模块,同时启动,同时读出。不过,同时读出的多个字在总线上需要分时传送。对连续字的成块传送可实现多模块流水式并行存取,大大提高存储器的带宽。

图3-14是按低位交叉编址的四个模块结构示意图。程序/数据连续存放在相邻存储体中,显然低位地址用来表示体号,高位地址为体内地址。这种编址方法又叫作模N编址,N等于模块数,表3-1列出了模4交叉编址的地址号。一般模块数N取2的整数次幂,可以使硬件电路比较简单。有的机器为了减少存储器冲突,采用质数个模块,如我国银河机的N为31,其硬件实现比较复杂。

图3-14 按低位交叉编址的四个模块存储器结构

表3-1 模4交叉编址

多体模块结构的存储器采用交叉编址后,可以在不改变每个模块存取周期的前提下,提高存储器的带宽。图3-15示意了四个存储模块交叉访问的时间关系,负脉冲为启动每个存储体的工作信号。虽然对每个模块而言,存取周期均未缩短,但由于CPU交叉访问各个模块,最终在一个存取周期的时间内,实际上向CPU提供了4个存储字。如果每个模块存储字长为32位,则在一个存取周期内,存储器向CPU提供32×4=128位二进制代码,大大加宽了存储器的带宽。

图3-15 四个存储模块交叉访问的时间关系

多体模块不仅要与CPU交换信息,还要与各种辅助存储器、外围设备乃至I/O处理机交换信息。因此,在某一时刻,决定主存究竟与哪个部件交换信息,必须由存储器控制部件来承担,存储器控制部件具有合理安排各部件请求访问的顺序以及控制主存读写操作的功能,它由排队器、控制线路、节拍发生器及标记触发器等组成。(https://www.xing528.com)

下面做定量分析:假如各模块字长等于数据总线宽度,模块存取一个字的存储周期为T,总线传送周期为τ,存储器的交叉模块数为N,为了实现流水线方式存取,应当满足

T=Nτ

即成块传送可按r间隔流水方式进行,也就是每经过τ时间延迟后启动下一个模块。N=T/τ称为交叉存取度。交叉存储器要求其模块数必须大于或等于N,以保证启动某模块后经Nτ时间再次启动该模块时,它的上次存取操作已经完成。这样,连续读取N个字所需的时间为

t1=T+(N-1)τ

而常规存储器中连续读取N个字所需时间为

t2=NT

显然,t1>t2。可见,多体交叉存储器的带宽确实大大提高了。

例3-1:设存储器容量为32字,字长64位,模块数N=4,分别用常规方式和交叉方式进行存储器组织。存储周期T=200ns,数据总线宽度为64位,总线传送周期τ=50ns。问常规存储器和交叉存储器的带宽各是多少?

解:常规存储器和交叉存储器连续读出N=4个字的信息总量都是

q=64位×4=256位

常规存储器和交叉存储器连续读出4个字所需的时间分别是

t2=NT=4×200ns=800ns=8×10-7s

t1=T+(N-1)τ=200ns+3×50ns=350ns~3.5×10-7s

常规存储器和交叉存储器的带宽分别是

W2=q/t2=256÷(8×10-7)=32×107(b/s)

W1=q/t1=256÷(3.5×10-7)=73×107(b/s)

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。