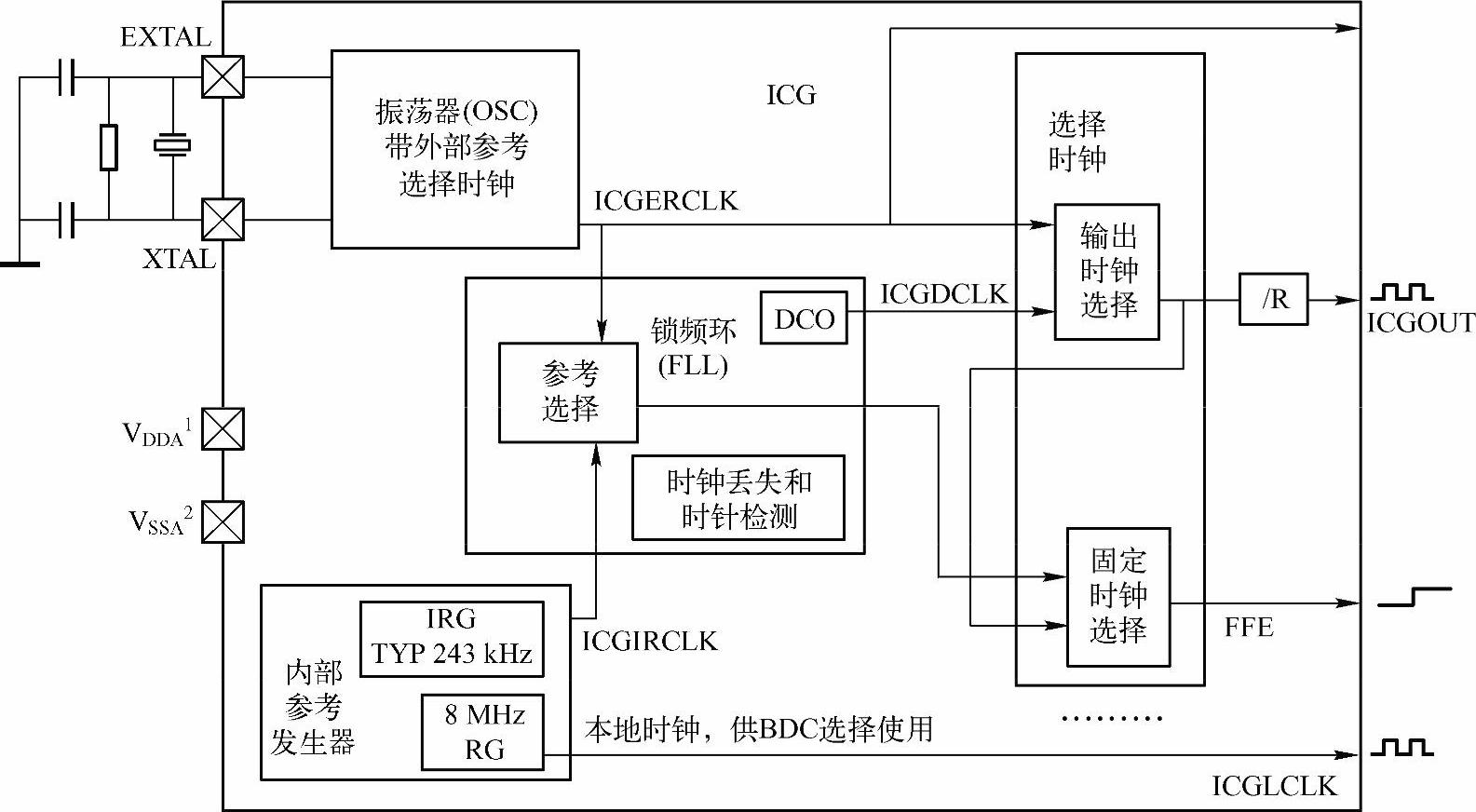

HCS08微控制器的内部时钟发生器ICG模块,采用锁频环技术FLL和内部倍频技术等,可在无须任何外界时钟发生器的情况下,通过软件设置实现高达20 MHz的内部总线时钟频率。内部时钟发生器ICG模块的功能结构如图7-2所示,与外部连接时复用PTG6和PTG5两个I/O引脚。ICG由4个子模块构成:振荡器模块、内部参考时钟发生器、锁频环(FLL)和时钟选择模块。

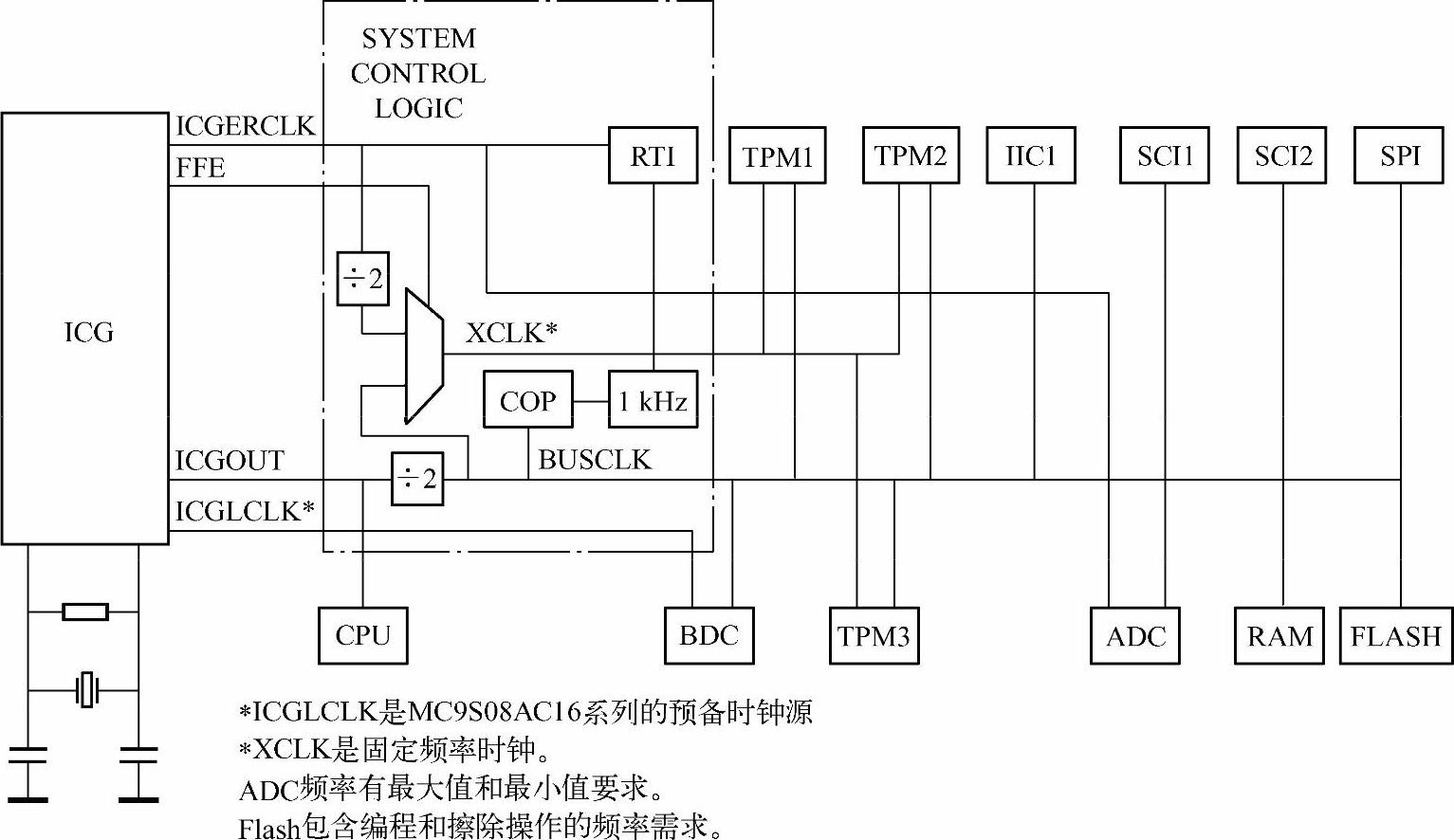

图7-1 系统时钟分配结构图

图7-2 内部时钟发生器(ICG)模块的功能结构图

1.振荡器模块

用于外接晶体振荡器,可通过软件选择两种晶体振荡器频率范围:32~100kHz低频范围或1~16MHz高频范围,以获得最佳的启动和稳定性能,还可以外接方波时钟作为系统时钟,这样可以获得非常高的时钟精度。通过设置ICG模块控制寄存器ICGC1中的HGO位,振荡器模块输出引脚XTAL可以被配置为低功耗模式或高振幅模式。为了降低功耗,可以选择采用低功耗模式以限定晶体引脚XTAL输出电压的峰峰值在1V范围内;如果是在噪声环境中使用,那么可以选择高增益模式。

2.内部参考时钟发生器

由两个可控时钟源组成:一个产生大约8 MHz的ICGLCLK时钟,可作为背景调试控制器的局部时钟;另一个内部时钟参考源ICGIRCLK的典型值为243kHz,可作为FLL模的参考输入。

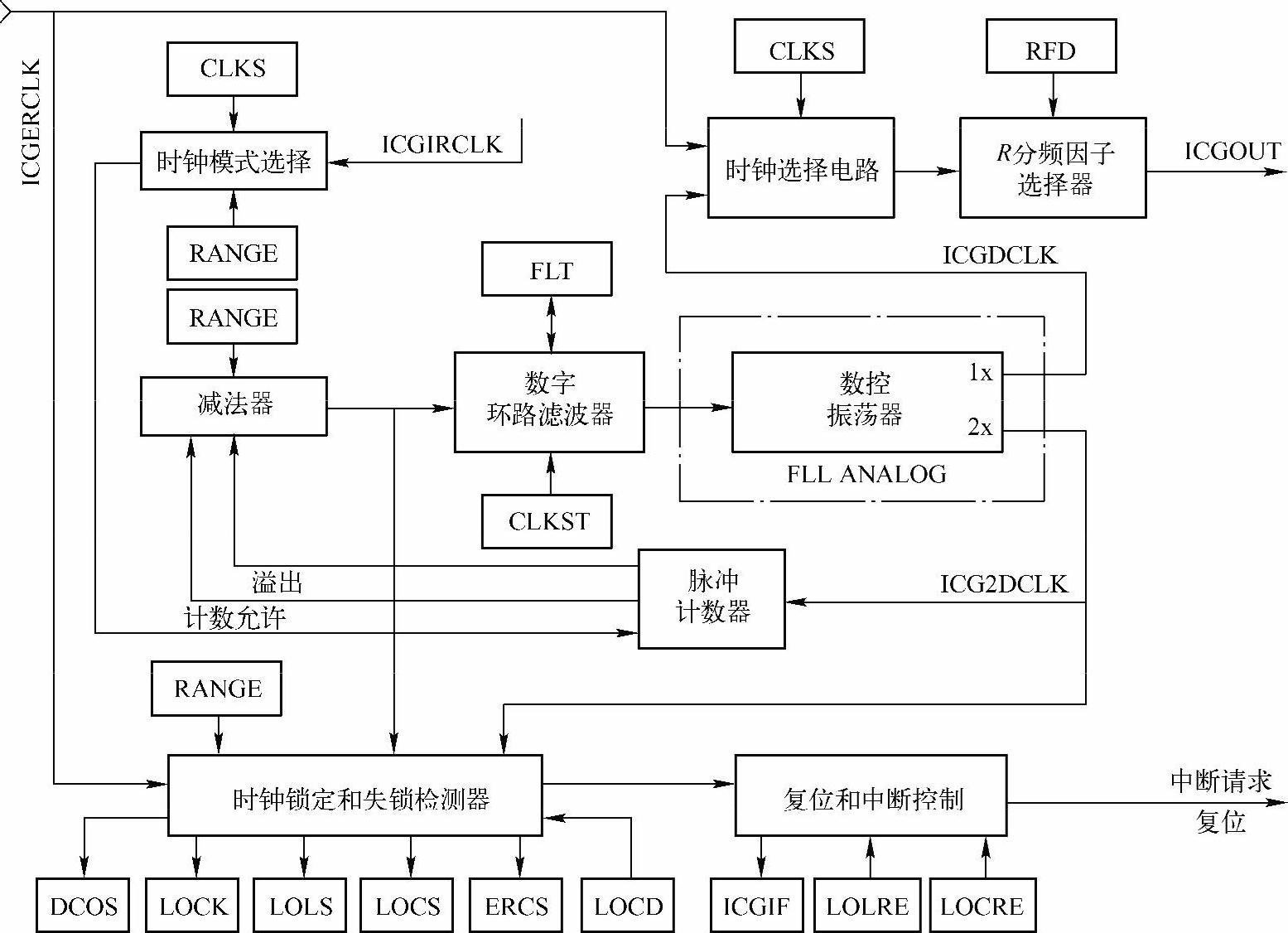

3.锁频环(Frequency-Locked Loop,FLL)

FLL锁频环用于倍频内部或者外部时钟源,可以通过对内部时钟源ICGIRCLK(243kHz)或外部时钟源ICGERCLK倍频,得到一个非常高且稳定的频率输出,锁频环模块和时钟选择模块的结构框图如图7-3所示。FLL由3个主要模块组成:时钟参考选择、数控振荡器和用于比较其他两个模块输出的数字环路滤波器。FLL非常类似于锁相环(PLL),区别在于:PLL是基于参考时钟和数控振荡器时钟的相位差调节输出,而FLL通过比较数控振荡器时钟和参考时钟的频率来工作。锁频环比较输入信号和数控振荡器输出信号之间的频率差,进而通过误差来控制调整数控振荡器的频率,达到与输入信号同频。在锁频环中数字环路滤波器的性能尤为重要。当环路工作时,如果输入信号与数控振荡器输出之间的频差为零,则锁频环进入频率锁定状态。在锁频环控制寄存器中提供频率锁定和失锁的状态位,以指示当前状态,另外,FLL还可以监控外部的参考时钟和信号是否有效。

图7-3 锁频环模块和时钟选择模块的结构框图

4.时钟选择模块(https://www.xing528.com)

该模块用于选择不同的时钟源连接到系统时钟上,如图7-2、图7-3所示。ICGDCLK是FLL输出的倍频时钟,ICGERCLK是晶体或外部时钟源参考时钟频率,FFE(Fixed Frequency Enable)是一控制信号,用于控制系统固定时钟(XCLK),ICGLCLK是背景调试控制器(BDC)的时钟源。

ICG模块的输出时钟有4个时钟:ICGOUT、FFE、ICGLCLK和ICGERCLK。

1)ICG的主输出为ICGOUT,它用于生成CPU和系统总线的时钟信号。CPU的时钟频率等于ICGOUT的频率,而总线时钟的频率等于ICGOUT频率的1/2。即

fCPU=fICGOUT

fBUS=fICGOUT/2

ICGOUT输出可以源自下列时钟源之一。

●外部晶体振荡器。

●外接时钟源。

●锁频环(Frequency Locked Loop,FLL)予模块中数控振荡器(DCO)的输出。

ICGOUT输出为上述哪种时钟源,由ICG模块的工作模式决定,或者由ICGC1寄存器串的控制位CLKS决定。

2)FFE是ICG内部产生的一个控制信号,用于选定图7-2所示的固定时钟XCLK的频率fXCLK。如果fICGOUT>4fICGERCLK,则FFE为l且fXCLK=fICGERCLK/2;否则FFE为0且fXCLK=fBUSCLK。

3)ICGLCLK,当总线时钟频率比较低的时候,开发工具可以选择这个大约8MHz的内部自供时钟源ICGLCLK来加快BDC通信。

4)ICGERCLK,外部参考时钟ICGERCLK可被用于实时中断(Real-Time Interrupt,RTI)时钟源,也可用于ADC模块时钟ALTCLK的时钟源。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。