6 A/D、D/A转换器的应用

6.1 A/D、D/A转换器的工作原理

6.1.1 D/A转换器的工作原理

D/A转换器(digital to analog converter)是一种能把数字量转换成模拟量的电子器件;A/D转换器(analog to digital converter)则相反,它能把模拟量转换成相应的数字量。在微机控制系统中,经常要用到A/D和D/A转换器。

D/A转换器按工作原理分为T形电阻网络、倒T形电阻网络、权电阻网络三种形式。

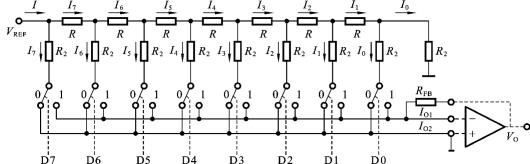

倒T形电阻网络D/A转换器的工作原理如图6.1所示。

图6.1 倒T形电阻网络D/A转换器工作原理图

当输入数据D7~D0为1111 1111B时,有:

若R FB=R,则:

![]()

=-(V REF/28)×(27+26+25+24+23+22+21+20)

输出电压VO的大小与数字量具有对应的关系。

D/A转换器的主要性能指标如下。

(1)分辨率,是指输入数字量的最低有效位(LSB)发生变化时,所对应的输出模拟量(电压或电流)的变化量。它反映了输出模拟量的最小变化值。分辨率与输入数字量的位数有确定的关系,可以表示成FS/2n。FS表示满量程输入值,n为二进制位数。对于5 V的满量程,采用8位的D/A时,分辨率为5 V/256=19.5 m V;当采用12位的D/A时,分辨率则为5 V/4096=1.22 m V。显然,位数越多分辨率就越高。

(2)线性度(也称非线性误差),是实际转换特性曲线与理想特性直线之间的最大偏差,常以相对于满量程的百分数表示。如±1%是指实际输出值与理论值之差在满刻度的±1%以内。

(3)绝对精度(简称精度),是指在整个刻度范围内,任一输入数码所对应的模拟量实际输出值与理论值之间的最大误差。绝对精度是由D/A转换器的增益误差(当输入数码为全1时,实际输出值与理想输出值之差)、零点误差(输入数码为全0时,D/A转换器的非零输出值)、非线性误差和噪声等引起的。绝对精度(即最大误差)应小于1个LSB。

(4)建立时间,是指输入的数字量发生满刻度变化时,输出模拟信号达到满刻度值的±1/2LSB所需的时间。该指标是描述D/A转换速率的一个动态指标。电流输出型D/A转换器的建立时间短。电压输出型D/A转换器的建立时间主要取决于运算放大器的响应时间。根据建立时间的长短,可以将D/A转换器分成高速(<1μs)、中速(100~1μs)、低速(≥100μs)几档。

应当注意,精度和分辨率具有一定的联系,但概念不同。D/A转换器的位数多时,分辨率会提高,对应于影响精度的量化误差会减小。但其他误差(如温度漂移、线性不良等)的影响仍会使D/A转换器的精度变差。

6.1.2 典型的D/A转换器DAC0832

DAC0832芯片由8位输入寄存器、8位D/A转换寄存器、8位D/A转换及控制电路三部分组成,如图6.2所示。DAC0832芯片具备双缓冲、单缓冲和直通三种输入方式,以便适应于各种需要,如要求多路D/A异步输入、同步转换等。D/A转换结果采用电流形式输出,若需要相应的模拟电压信号,可通过一个高输入阻抗的线性运算放大器实现。运放的反馈电阻可通过RFB端引用片内固有电阻,也可外接。DAC0832属于倒T形电阻网络D/A转换器,内部无运算放大器。

DAC0832的主要技术指标:

(1)分辨率8位;

(2)电流建立时间1μs;

(3)只需在满量程下调整其线性度;

(4)可单缓冲、双缓冲或直接数字输入;

(5)低功耗20 m W;

(6)单一电源+5 V~+15 V。

图6.2 DAC0832内部结构图

D0~D7:数据输入线,TLL电平。

ILE:数据锁存允许控制信号输入线,高电平有效。

CS:片选信号输入线,低电平有效。

WR1:为输入寄存器的写选通信号,低电平有效。

XFER:数据传送控制信号输入线,低电平有效。

WR2:为D/A转换寄存器写选通输入线,低电平有效。

IOUT1:电流输出线。当输入全为1时,IOUT1最大。

IOUT2:电流输出线。其值与IOUT1之和为一常数。

RFB:反馈信号输入线,芯片内部有反馈电阻。

VCC:电源输入线(+5 V~+15 V)。

VREF:基准电压输入线(-10 V~+10 V)。

AGND:模拟地,模拟信号和基准电源的参考地。

DGND:数字地,两种地线在基准电源处共地比较好。

6.1.3 A/D转换器的工作原理

A/D转换器按工作原理分为积分型、逐次逼近型、并行比较型/串并行型、Σ-Δ调制型等。积分型A/D转换器工作原理是将输入电压转换成时间(脉冲宽度信号)或频率(脉冲频率),然后由定时器/计数器获得数字值。其优点是用简单电路就能获得高分辨率,但缺点是由于转换精度依赖于积分时间,因此转换速率极低。初期的A/D转换器大多采用积分型,现在逐次比较型已逐步成为主流。下面重点讲述逐次逼近型A/D转换器的工作原理。

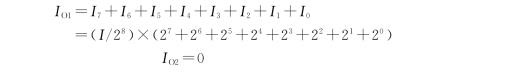

逐次逼近型A/D转换器采用对分搜索原理来实现A/D转换,逻辑框图如图6.3所示。

逐次逼近转换过程与用天平称重物的过程非常相似。天平称重物的过程是,从最重的砝码开始试放,与被称物体进行比较,若物体重于砝码,则该砝码保留,否则移去。再加上第二个次重砝码,由物体的重量是否大于砝码的重量决定第二个砝码是留下还是移去。照此一直加到最小一个砝码为止。将所有留下的砝码重量相加,就得此物体的重量。仿照这一思路,逐次比较型A/D转换器,就是将输入模拟信号与不同的参考电压进行多次比较,使转换所得的数字量在数值上逐次逼近输入模拟量对应值。

图6.3 逐次逼近型A/D转换器逻辑框图

图6.3所示的是逐次逼近型A/D转换器的工作原理:启动信号START发出后,在第一个时钟脉冲作用下,控制逻辑使N位寄存器的最高位置1,其他位置0,其值送入D/A转换器。输入电压首先与D/A转换器输出电压(VREF/2)相比较,如果VIN ≥VREF/2,转换器输出为1;若VIN<VREF/2,则为0。比较结果存于数据寄存器的Dn-1位。然后在第二个脉冲作用下,N位寄存器的次高位置1,其他位置0。由于最高位已存1,则此时VN=(3/4)VREF。于是VIN再与(3/4)VREF相比较,如果VIN≥(3/4)VREF,则次高位Dn-2存1,否则Dn-2存0……依此类推,逐次比较得到输出数字量。

A/D转换器的主要技术指标如下。

(1)A/D转换器的分辨率是指使输出数字量变化一个相邻数码所需输入模拟电压的变化量,常用二进制的位数表示。例如,12位A/D转换器的分辨率就是12位,或者说分辨率为满刻度FS的1/212;一个5 V满刻度的12位A/D转换器能分辨输入电压变化的最小值是5 V×1/212=1.22 m V。

(2)偏移误差是指输入信号为零时,输出信号不为零的值,所以又称为零值误差。假定A/D转换器没有非线性误差,则其转换特性曲线各阶梯中点的连线必定是直线,这条直线与横轴相交点所对应的输入电压值就是偏移误差。

(3)满刻度误差又称为增益误差。A/D转换器的满刻度误差是指满刻度输出数码所对应的实际输入电压与理想输入电压之差。

(4)线性度有时又称为非线性度,它是指转换器实际的转换特性曲线与理想直线的最大偏差。

(5)绝对精度是指在一个转换器中,任何数码所对应的实际模拟量输入与理想模拟量输入之差的最大值。对于A/D转换器而言,可以在每一个阶梯的水平中点进行测量,它包括了所有的误差。

(6)A/D转换器的转换速率是指能够重复进行数据转换的速度,即每秒转换的次数。而完成一次A/D转换所需的时间(包括稳定时间),则是转换速率的倒数。

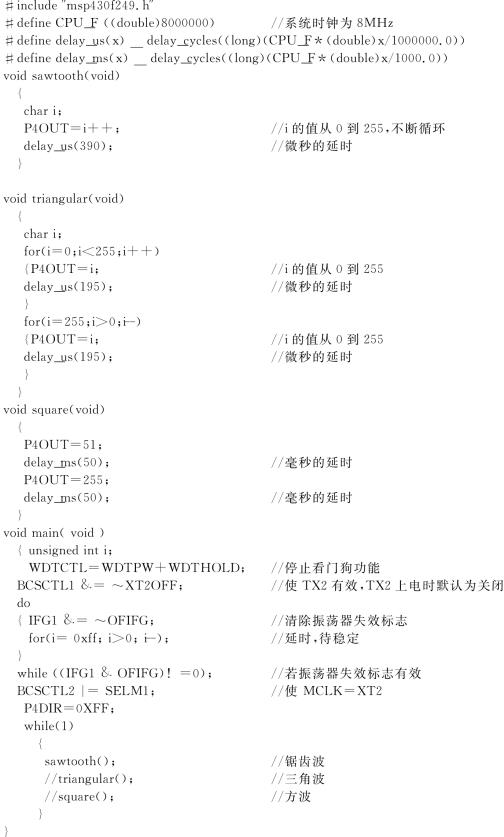

实例6.1 D/A转换器应用一:锯齿波、三角波和方波发生器

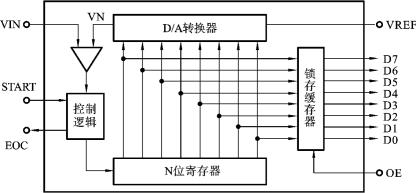

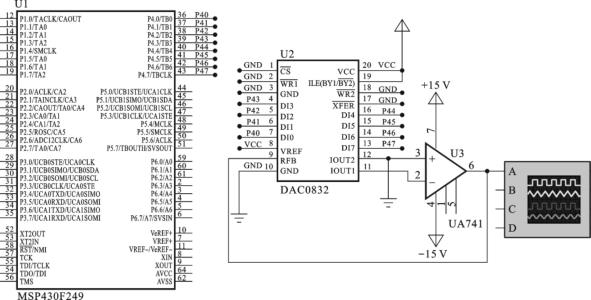

任务要求:以MSP430F249为控制核心,DAC0832为数模转换器,设计一个简易波形发生器,分别产生锯齿波、三角波和方波,周期均为100 ms,产生的波形如图6.4所示。

图6.4 锯齿波、三角波和方波示意图

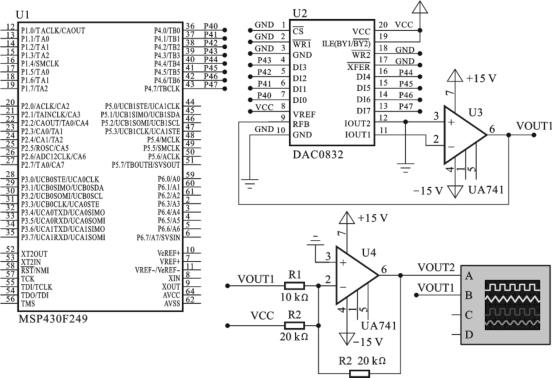

1)硬件电路设计

数模转换器采用通用的8位D/A转换芯片DAC0832,DAC0832接成直通方式工作,工作和参考电源均为+5 V。反相放大电路采用通用运放UA741,工作电源为±15 V,反馈电阻直接采用DAC0832的内部电阻。MSP430F249单片机的P4端口作为数据输出口,D/A的转换结果由仿真软件的虚拟示波器进行观察。系统硬件电路如图6.5所示。

图6.5 简易波形发生器硬件电路图

2)程序设计

为了精确控制输出波形的周期,单片机CPU时钟采用XT2外接8 MHz晶振。设置MSP430F249单片机的P4端口为输出,P4端口输出的数据由小到大,例如从0到0xFF就能产生锯齿波。要求产生的锯齿波周期为100 ms,因此,单片机输出的每个数据保持时间为100000μs/256=390.625μs;P4端口输出的数据由小到大,再由大到小,例如从0加1变化到0xFF,再从0x FF减1变化到0就能产生三角波,单片机输出的每个数据保持时间为锯齿波的一半,即195μs;方波的高电平为-1 V,低电平为-5 V,对应的P4端口数据分别为51和255,方波的高电平和低电平保持的时间各为50 ms。

在IAR软件MSP430的编译器里,可以利用它内部的延时子程序来实现想要的高精度软件延时,方法如下:

将以下代码复制到*.C源文件中。

#define CPU_F((double)8000000)

#define delay_us(x)delay_cycles((long)(CPU_F*(double)x/1000000.0))

#define delay_ms(x)delay_cycles((long)(CPU_F*(double)x/1000.0))

在#define CPU_F((double)8000000)语句里8000000修改成当前MSP430 CPU的主频频率,即CPU的MCLK,单位为Hz。本例中的8000000为MCLK=8 MHz的意思。_delay_cycles()是编译系统函数。

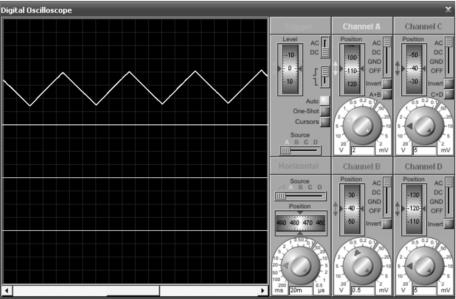

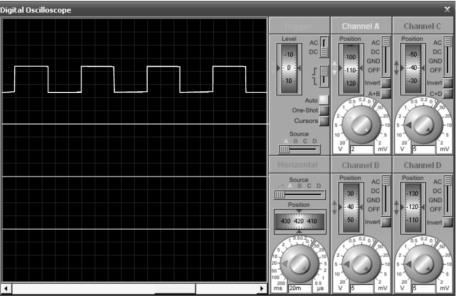

3)仿真结果与分析

通过子程序调用,分别仿真运行后得到仿真结果如图6.6~图6.8所示,三种波形的幅值、周期均满足课题要求。

图6.6 周期为100 ms的锯齿波

图6.7 周期为100 ms的三角波

思考:1.本电路运放需要±15 V电源,请问能采用单电源运放方式完成本课题任务吗?

2.本电路输出电压为负,要得到正输出电压怎么实现?

图6.8 周期为100 ms的方波

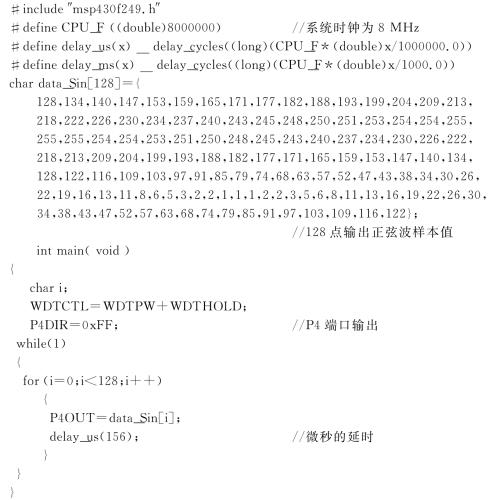

实例6.2 D/A转换器应用二:正弦波发生器

任务要求:在实例6.1简易波形发生器的基础上实现正弦波信号输出,最大值±5 V,频率为50 Hz。

1)硬件电路设计

图6.5所示的简易波形发生器硬件电路只能输出-5 V~0 V电压,本课题要求输出最大值±5 V正弦信号,运放电路采用两级设计,第二级为加法电路,可以实现双极性输出。正弦波发生器电路如图6.9所示,当VOUT1=0时,VOUT2=+5 V;当VOUT1=-2.5 V时,VOUT2=0;当VOUT1=-5 V时,VOUT2=-5 V。因此,图6.9所示的双极性电路就能实现输出±5 V电压信号。

2)程序设计

由单片机产生正弦波信号的一般方法是:先建立一张正弦波数据表,单片机按查表方式经D/A输出得到正弦波信号。实例中采用的D/A转换器是8位的,因此正弦波数据表最多有256个值。一般单片机输出64点或128点,经D/A电路后得到的正弦波波形就比较完美了。下面以128点输出为例完成本课题任务,要求正弦波频率为50 Hz,那么周期就是20 ms,20000μs/128=156.25μs,即单片机输出的每个数据保持156μs。

为了得到128点的正弦波数据表,我们在Matlab环境中新建如下的m文件。

Matlab语句说明:round()为取整数函数,四舍五入,D/A转换值只能是正数;fopen()和fclose()分别为文件打开和关闭函数。以上程序运行后,可以到d盘根目录中找到sin256.txt文件,得到正弦波数据。

图6.9 正弦波发生器电路图

3)仿真结果与分析

仿真结果如图6.10所示。图中A通道是最大值范围±5 V、频率50 Hz的正弦波信号;B通道是最大值范围-5 V~0 V、频率50 Hz的正弦波信号;A通道和B通道输出信号的相位相差180°。

图6.10 D/A输出的正弦波信号

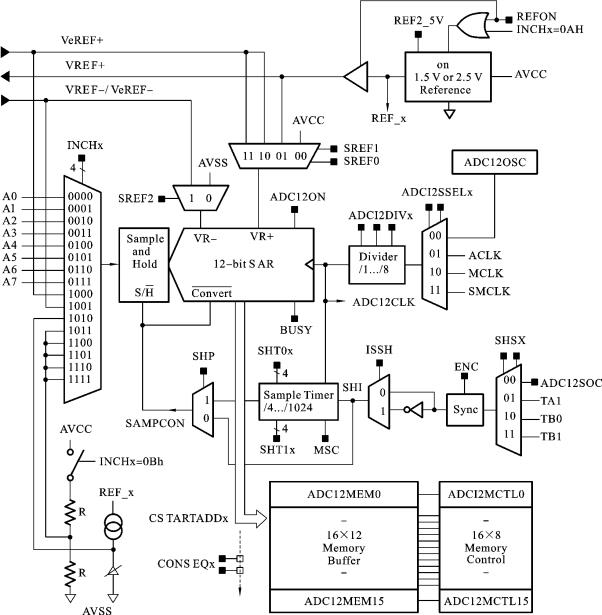

6.2 MSP430F249的A/D转换器

MSP430F249单片机内置了ADC12模块,ADC12是一个12位精度的A/D转换模块。从图6.11所示的ADC12结构图中可以看出,ADC12模块中是由以下部分组成:输入的16路模拟开关、ADC内部电压参考源、ADC12内核、ADC时钟源部分、采集与保持/触发源部分、ADC数据输出部分、ADC控制寄存器等。

1)输入的16路模拟开关

16路模拟开关选择外部的8路模拟信号输入和内部4路参考电源输入。外部8路从A0~A7输入,主要是外部测量时的模拟变量信号。内部4路分别是1路VeREF+,外部参考电源的正端;1路VREF-/VeREF-,内部/外部参考电源负端;1路(AVCCAVSS)/2电压源;1路内部温度传感器源。片内温度传感器可以用于测量芯片上的温度,而其他电源参考源输入可以用作ADC12的校验,在设计时作自身校准。

2)ADC内部电压参考源

ADC电压参考源是给ADC12内核作为基准信号用的,这是ADC必不可少的一部分。在ADC12模块中,基准电压源可以通过软件来设置6种不同的组合,包括VR+(有3种)AVCC、VREF+,VeREF+;VR-(有2种)AVSS、VREF-/VeREF-。

3)ADC12内核

ADC12模块的内核是共用的,通过前端的模拟开关分别完成采集输入。ADC12是一个精度为12位的ADC内核。内核在转换时会用到两个参考基准电压:一个是最大值,当模拟开关输出的模拟变量大于或等于最大值时ADC内核的输出数字量为满量程,也就是0xfff;另一个则是最小值,当模拟开关输出的模拟变量小于或等于最小值时ADC内核的输出数字量为最低量程,也就是0x00。而且,这两个参考基准电压是可以通过软件来编程设置的。

图6.11 ADC12结构图

4)ADC时钟源部分

ADC12模块的时钟源分别有ADC12OSC、ACLK、MCLK、SMCLK。通过编程可以选择其中之一的时钟源,同时还可以适当地分频。

5)采集与保持/触发源部分

ADC12模块中的采集与保持电路较好,采用不同的设置应用灵活。

6)ADC数据输出部分

ADC内核在每次完成转换时都会将相应通道上的输出结果存储到相应通道缓冲单元中,共有16个通道缓冲单元。同时,16个通道的缓冲单元有着相对应的控制寄存器,以实现更灵活地控制。

ADC12模块采样与转换所需的时序控制有ADC12CLK转换时钟、SAMPCON采样及转换信号、SHT控制的采样周期、SHS控制的采样触发源、ADC12SSEL选择的内核时钟源、ADC12DIV选择的分频系数。具体如何设置,见寄存器说明部分。

ADC12模块有4种转换模式:单通道单次转换、序列通道单次转换、单通道多次转换和序列通道多次转换。它们由寄存器ADC12CTL1中的CONSEQx位进行选择。(https://www.xing528.com)

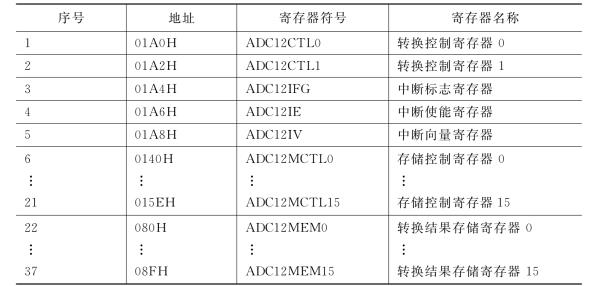

7)ADC控制寄存器

ADC12模块的所有寄存器如表6-1所示。

表6-1 ADC模块的寄存器

(1)ADC12控制寄存器0,ADC12CTL0,每个寄存器的格式如表6-2所示。

表6-2 ADC12控制寄存器0

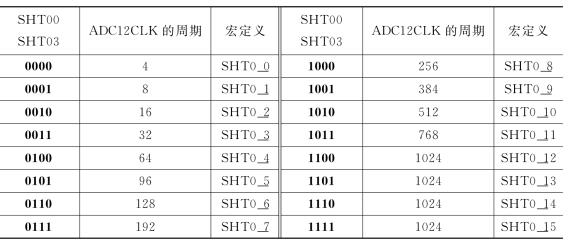

SHT0x(x=0~3)定义ADC12MEM0~ADC12MEM7的采样保持时间。

SHT1x(x=0~3)定义ADC12MEM8~ADC12MEM15的采样保持时间。

SHT00、SHT03的采样周期如表6-3所示。

表6-3 采样周期

注:SHT10~SHT13的宏定义为SHT1_0~SHT1_15,SHT1定义的ADC12CLK的周期同上表。

MSC 多次采样转换位,序列通道或单通道多次转换模式有效。置0表示每次采样转换过程需要SHI信号的上升沿来触发;置1表示SHI信号的第一个上升沿触发采样定时器,但随后的采样转换在上次转换完成后自动进行。

REF2.5V 内部参考电压的电压值选择位:置0时选择1.5 V内部参考电压;置1时选择2.5 V内部参考电压。

REFON 参考电压控制:置0时内部参考电压发生器关闭;置1时内部参考电压发生器打开。

ADC12ON ADC12 内核控制位:置0时关闭ADC12内核;置1时打开ADC12内核。

ADC12OVIE 溢出中断允许位:置0时溢出中断允许;置1时溢出中断禁止。当ADC12MEMx中原有的数据还没有被读出,而现在又有新的转换结果数据要写入时,则会发生溢出。如果相应的中断允许,则会发生中断请求。

ADC12TVIE 转换时间溢出中断允许位:置0时没发生转换时间溢出;置1时发生转换时间溢出。当前转换还没有完成时,如果又发生一次采样请求,则会发生转换时间溢出。如果允许中断,则会发生中断请求。

ENC 转换允许位:置0时转换禁止;置1时转换允许。只有在该位为高电平时,才能用软件或外部信号启动转换。

ADC12SC 启动转换控制位:置0时不进行采样转换;置1时启动采样转换。

(2)ADC12控制寄存器1,ADC12CTL1,寄存器格式如表6-4所示。

表6-4 ADC12控制寄存器1

CSTARTADDx(x=0~3) 指定转换结果存放的存储器起始地址:该4位表示的二进制数0~15分别对应ADC12MEM0~ADC12MEM15,该4位定义了单次转换地址或序列转换的首地址。

SHSx(x=0、1) 采样保持的信号源选择位,格式如表6-5所示。

表6-5 信号源选择位

SHP采样信号(SAMPCON)选择控制位:置0时SAMPCON信号来自采样触发输入信号;置1时SAMPCON信号来自采样定时器。

ISSH采样输入信号方向控制位:置0时采样输入信号为同向输入;置1时采样输入信号为反向输入。

ADC12DIVx(x=0~2) ADC12时钟源分频因子选择位,格式如表6-6所示。

表6-6 ADC12时钟源分频因子选择位

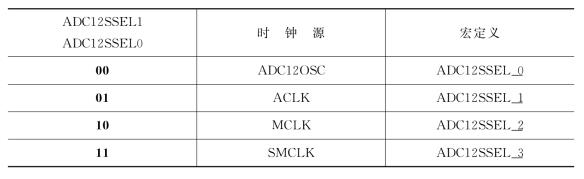

ADC12SSELx(x=0、1) ADC12时钟源选择位,格式如表6-7所示。

表6-7 ADC12时钟源选择位

CONSEQx(x=0、1) ADC12转换模式选择位,格式如表6-8所示。

表6-8 ADC12转换模式选择位

ADC12BUSY ADC12忙标志位:置0时表示没有活动的操作;置1时表示ADC12正处于采样期间、转换期间或序列转换期间。

(3)转换结果存储寄存器共有16个,ADC12MEM0~ADC12MEM15,每个寄存器格式如表6-9所示。

表6-9 ADC12存储寄存器

注:16位转换结果只用低12位,高4位在读出时为0;12位转换结果是右对齐的。

(4)ADC12存储控制寄存器共有16个,ADC12MCTL0~ADC12MCTL15,这16个寄存器的格式都相同,每个寄存器的格式如表6-10所示。

表6-10 ADC12存储控制寄存器

EOS 序列结束控制位:置0时序列没有结束;置1时此序列中最后一次转换。

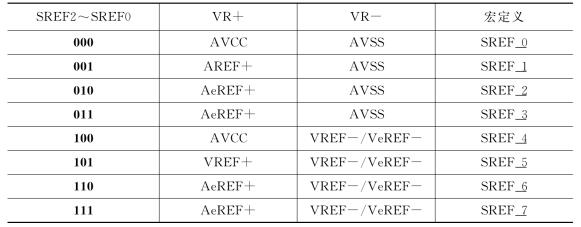

SREFx(x=0~2) 参考电压源选择位,格式如表6-11所示。

表6-11 SREFx参考电压源选择位

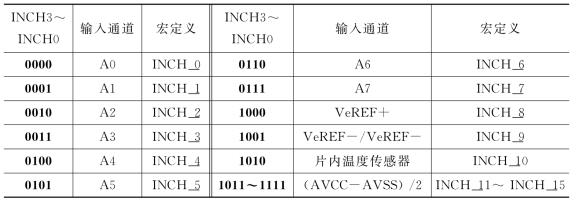

INCHx(x=0~3) 输入通道选择位,格式如表6-12所示。

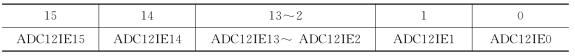

(5)ADC12中断使能寄存器,ADC12IE,格式如表6-13所示。

表6-13 中断使能寄存器

注:当ADC12IE0~ADC12IE15为0时,禁止相应的中断;为1时,允许相应的中断。

(6)ADC12中断标志寄存器,ADC12IFG,格式如表6-14所示。

表6-14 中断标志寄存器

注:当A/D转换结束,相应的寄存器有转换结果时,中断标志ADC12IFG0~ADC12IFG15建立。

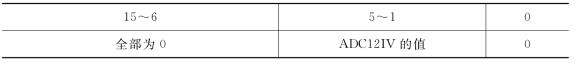

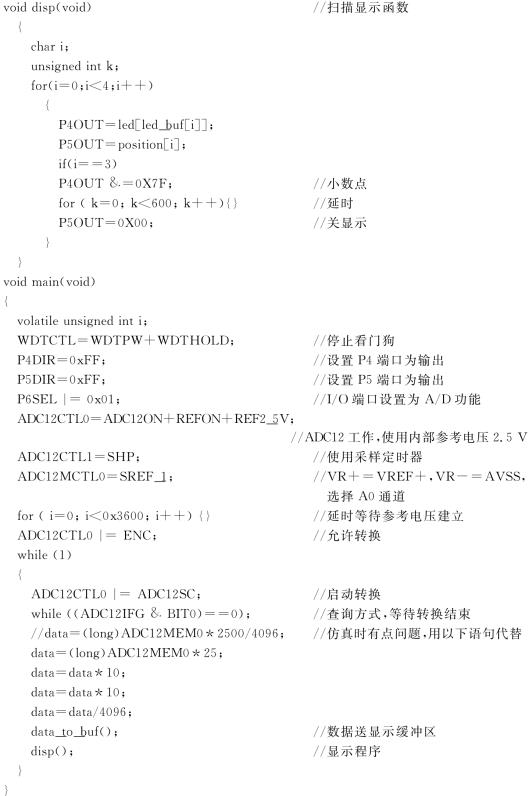

(7)ADC12中断向量寄存器,ADC12IV,格式如表6-15所示。

表6-15 中断向量寄存器

ADC12是一个多源中断,有18个中断标志(ADC12IFG.0~ADC12IFG.15、ADC12TOV、ADC12OV),但只有一个中断向量,格式如表6-16所示。

表6-16 中断向量寄存器的选择

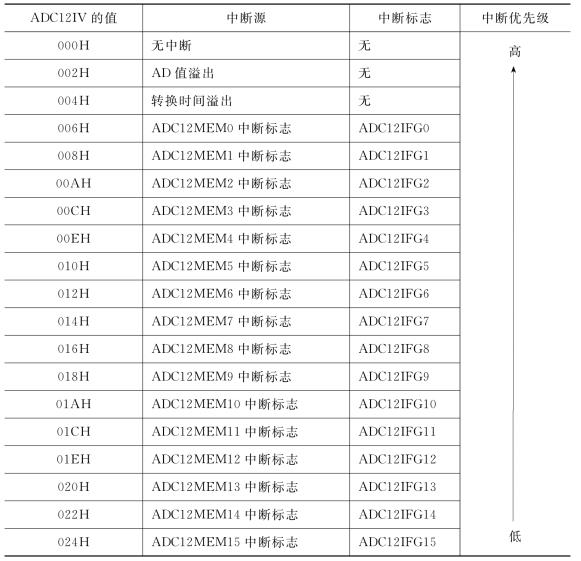

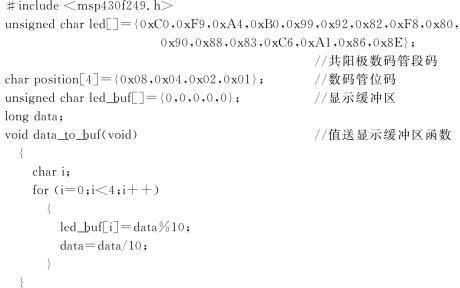

实例6.3 简易数字电压表

任务要求:设计一个简单的数字电压表,输入电压范围0~2.5 V,用4位数码管显示,3位小数。

1)硬件电路设计

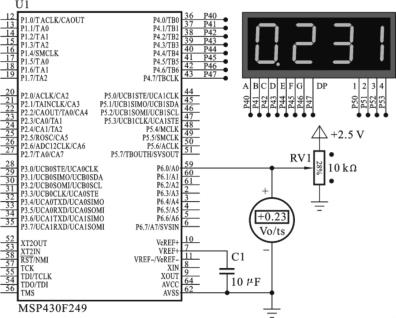

MSP430F249单片机的内部包含12位ADC模块。A/D转换参考电源采用内部2.5V作为基准,AVSS接地,VREF接10μF电容。外部被测电压+2.5 V经电位器接入A/D转换器的A0通道。显示电路采用4位数码管模块动态显示,P4端口为段码,P5端口低4位为位码。此电路仅做功能仿真,实际显示电路需加适当的驱动电路。硬件电路如图6.12所示。

图6.12 实例6.3硬件电路图

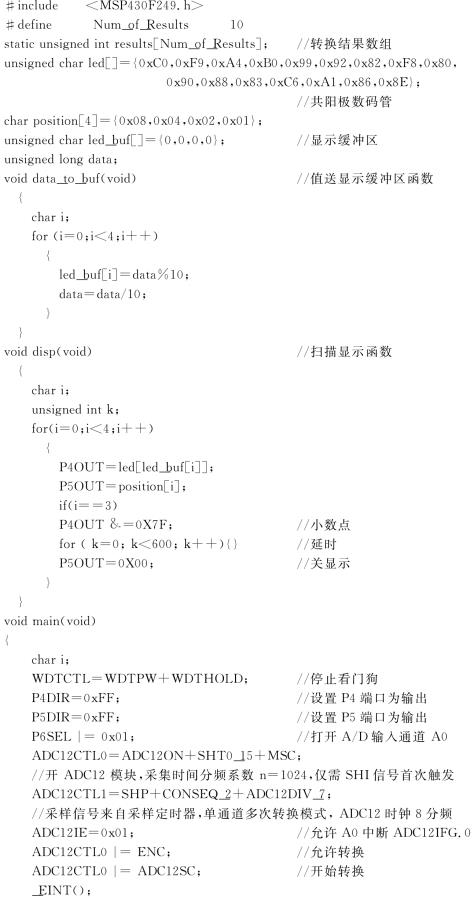

2)程序设计

A/D转换采用单通道单次转换模式,程序采用查询方式读取A/D转换值,然后进行量程转换和数码管动态显示。

A/D转换基本设置为允许ADC12内核工作,时钟源选用内部ADC12OSC,使用内部参考电压2.5V,上限VR+=VREF+,下限VR-=AVSS,选择A0通道,使用采样定时器,采样保持时间为4个ADC12CLK周期。12位A/D转换值为0~4095,量程转换公式为ADC12MEM0×2500/4096。显示部分为4位共阳极数码管电路,采用动态扫描方式,每位点亮2 ms(仿真时根据显示效果调整k值大小),不断循环。A/D采样最快200ksps,一般采样周期几十到几百微秒,不影响数码管动态显示。

3)仿真结果与分析

外部输入电压经电位器接入到A0采样通道,A/D转换器的基准为内部2.5 V。图6.13所示的电压表显示0.36 V,数码管显示0.357V,忽略误差,两者基本一致,可以认为A/D转换结果正确。多次调整电位器,观察数码管显示的电压值均符合实际所测电压值,因此,完成了“简单的数字电压表”课题任务。

思考:如果采用外部参考电压,硬件电路和程序设计如何改动?

图6.13 简单的数字电压表

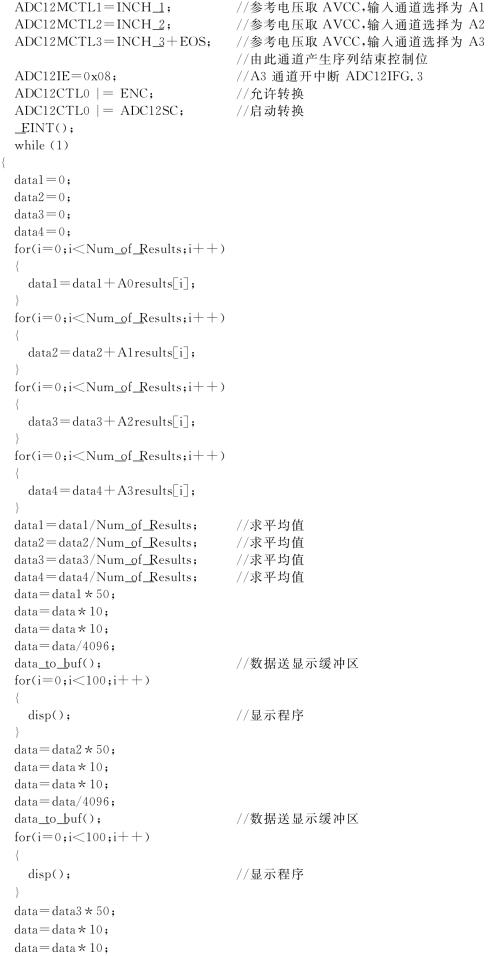

实例6.4 A/D采样:数字滤波算法

任务要求:要求在实例6.3的基础上,A/D采样转换10次,数据取算术平均值再显示,从而提高软件抗干扰能力。

分析说明:实例6.3中,A/D采样转换一次,数据就输出显示,实际应用时存在各种干扰因素,显示的数据可能不稳定,即输入电压不变,LED显示的数据不断变化。除了采用必要的硬件抗干扰措施外,一般在程序中也要采取抗干扰措施。

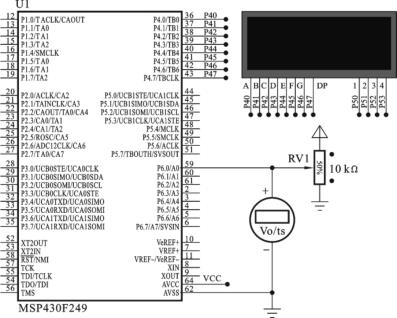

1)硬件电路设计

硬件电路如图6.14所示。

图6.14 实例6.4硬件电路图

2)程序设计

方法一:利用ADC12模块单通道多次转换模式设计。

3)仿真结果与分析

实例6.4的仿真结果如图6.15所示。

图6.15 实例6.4仿真结果图

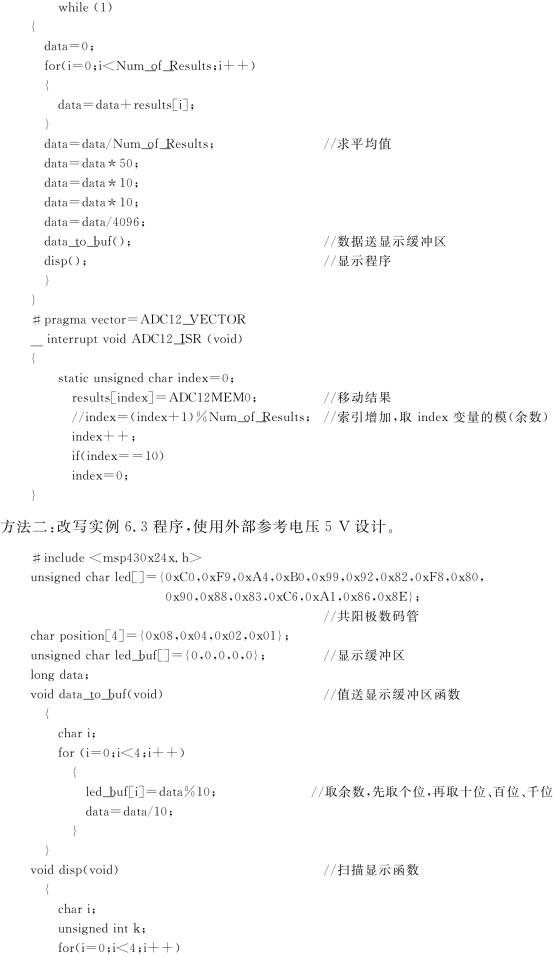

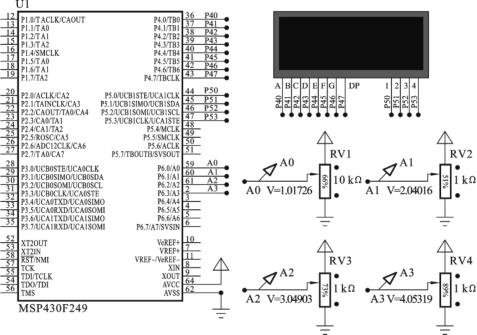

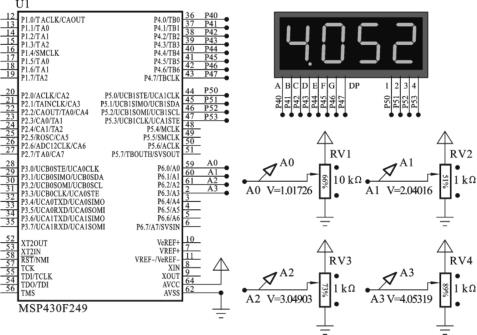

实例6.5 A/D采样:多路电压信号巡检

任务要求:4路电压信号输入,电压范围0~5 V。单片机A0~A3通道轮流采样转换,4位LED数码管轮流显示4路电压值。

1)硬件电路设计

A/D转换器参考电压为外部AVCC,即+5V电压,外部4路电压信号由电位器引入单片机A0~A3通道。显示电路采用4位数码管模块动态显示,P4端口为段码,P5端口低4位为位码。为了方便观察4路电压值,仿真电路中加入了4路电压探针。此电路仅做功能仿真,实际显示电路需加适当的驱动电路。硬件电路如图6.16所示。

图6.16 实例6.5硬件电路图

2)程序设计

采用ADC12序列通道多次采样模式,采样信号由SHI第一个上升沿触发,随后的采样转换会在上次转换结束后自动进行。为保证采样转换的抗干扰能力,每个通道数据取多次采样值的算术平均值,4路信号轮流显示。

3)仿真结果与分析

实例6.5的仿真结果如图6.17所示。

图6.17 实例6.5仿真结果图

思考与练习

1.某热处理炉温度变化范围为800℃~1300℃,经温度变换器变换为1 V~5 V电压送至12 位A/D转换器,A/D转换器的输入范围为0 V~5V。某时刻采样得到转换结果为3FFH,问此时炉内温度是多少度?写出中间过程。

2.设计一个简易波形发生器,通过按键设置可以分别产生三角波、锯齿波、正弦波等多种信号波形。输出信号的频率、幅度可以通过键盘设定调整。

3.完成实例6.3、实例6.4和实例6.5的程序调试与仿真,观察仿真结果。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。