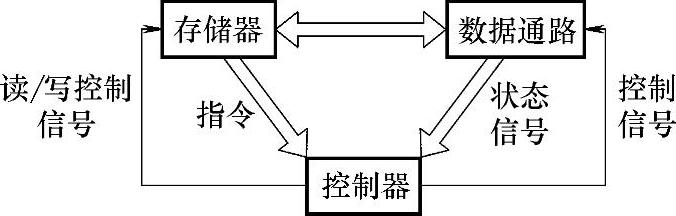

一个基本的CPU包括三部分功能:数据的存储、数据的运算和控制部分。与之相对应的硬件结构也分为三部分:存储器、数据通路和控制器。存储器、数据通路和控制器这三部分的基本关系如图4-21所示。

1.存储器

存储器中存放了要执行的指令和相应数据。存储器的读/写信号由控制器给出。存储器的地址来源有两个:程序计数器和指令寄存器。在取新指令时,用程序计数器的值作为存储器地址;在执行指令时,用指令中的地址部分作为存储器地址。

图4-21 CPU基本结构

2.数据通路

数据通路主要包括累加器、程序计数器和算术逻辑单元(ALU)。累加器用于保存参加运算的数据以及运算的中间结果。实际上,累加器也是寄存器,不过它有特殊性,即许多指令执行过程以累加器为中心。往往在运算指令前,累加器中存放一个操作数,指令执行后,由累加器保存运算结果。另外,I/O指令一般也通过累加器来完成。程序计数器指向下一条要执行的指令,由于程序一般存放在内存的一个连续区域,所以,顺序执行程序时,每取一个指令字节,程序计数器便加1。ALU是专门用来处理各种运算数据信息的,它可以进行加、减、乘、除算术运算和与、或、非、异或等逻辑运算。(https://www.xing528.com)

3.控制器

控制器产生相应的控制信号送到时序和控制逻辑电路,进而组合成外部电路所需要的时序和控制信号。这些信号送往其他部件,以控制这些部件协调工作。

以冯·诺依曼结构来实现RISC-CPU的设计,将数据和程序(指令序列)统一存放在一个数据存储器中。对图4-21中的结构进行细化,可以得到一个简单CPU的架构,如图4-22所示。该CPU采用总线结构,即控制器所需的指令、数据通路所需的数据都是从总线上得到的。

图4-22 CPU简单架构

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。