我们主要的假定是维持图7-2所示的8f2存储器单元。其中,阵列器件的宽度和长度都等于特征尺寸f。因此,不像逻辑电路中的器件,DRAM器件的设计中,等比例缩小并不是一个自由的参数。DRAM器件的缩小必须通过其他方法实现。为了充分理解这一概念,有必要分析阵列器件的边界条件。为了进行更全面的讨论,采用下述符号:VPP是选中单元的字线电压,VLL是未选中单元的字线电压,而VBB是阵列器件(不再使用p型阵列器件)的p阱电压。采用三阱工艺,其中阵列p阱位于n阱中;这可以对传送晶体管施加衬底偏置,从而提升阈值电压Vth,并且也可以将阵列与衬底噪声隔离,并且还能在一定程度上隔离电离粒子的影响。

DRAM泄漏要求是对阵列器件最严格的限制。DRAM的标准刷新周期为64ms。使用20fF的存储器电容和可承受300mV的泄漏损耗,则最终的总泄漏预算是100fA。如果将总预算的10%分配给器件,器件的泄漏就必须限制在10fA之下。由于泄漏电流随着温度升高而增加,因此要求在最高工作温度下器件的泄漏电流也不能超过10fA。和位线相连的存储单元出现最坏的关态条件是:相应的读出放大器激活,将位线拉低。可以得到

然而,器件不能仅仅只针对泄漏进行优化。最重要的是,读出电流必须足够高。简单的说,要求加在单元电容上的初始读出电压斜率为750mV/2n。在位线被充电到VAA/2时的读出条件下必须达到这个值,使器件进入源极跟随模式。由于阈值电压随温度的下降而增加,一般这个条件在低温时是最严格的。器件迁移率随着温度的增加而衰退不能补偿这种阈值电压效应。因此:

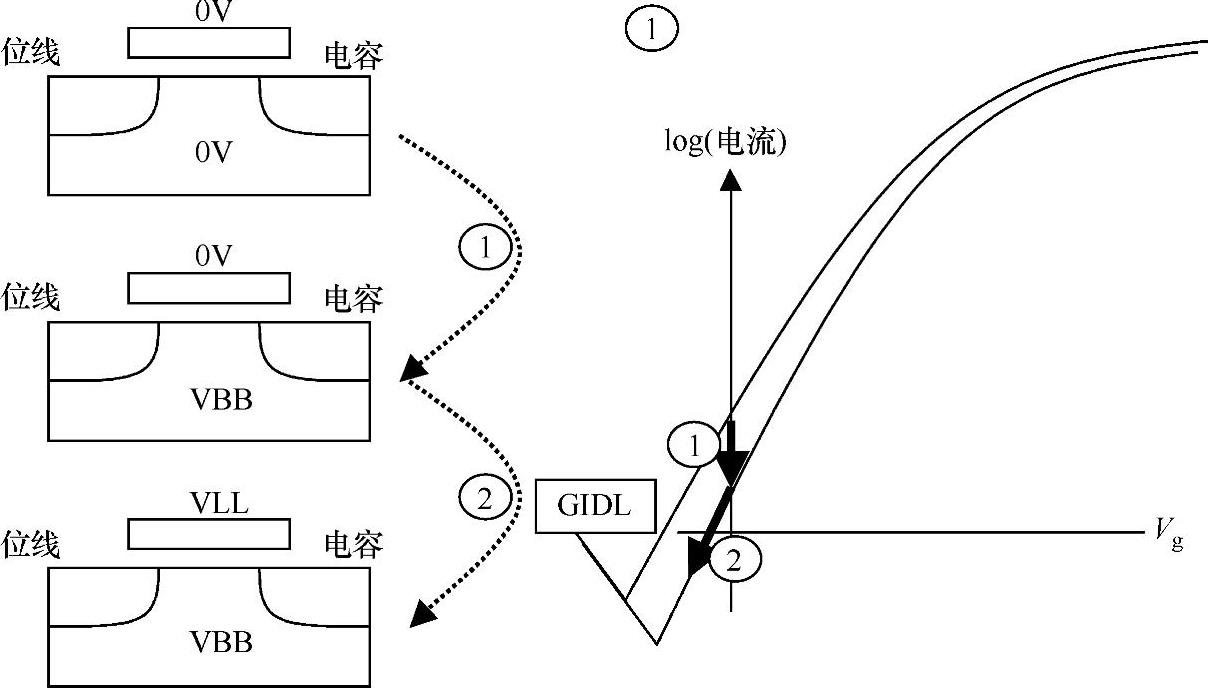

我们先总结满足泄漏要求的方法。图7-7说明了这种改善。在几代工艺中,许多标准DRAM使用负VBB。采用负VBB可以提升器件的阈值电压,因此将减小关态电流泄漏。然而,必须注意VBB也是存储节点n扩散的p阱电压。增加VBB将会增大二极管的结泄漏,所以必须仔细选择最优的设计点。

图7-7 控制阵列器件泄漏的电压工程。图右半边是采用对数坐标表示的传送器件电流,以着重显示亚阈区电流。左半边显示了新引入电压的过程。首先,加负的p阱电压VBB,改变了I-V曲线。在100nm节点附近,未选中器件的字线电压被设定为负值以获得较低的阈值电压,但是又不能太负,否则将进入GIDL区(https://www.xing528.com)

在100nm工艺时代,这种相当经典的方法被证明是不够的。作为一项新的改进,引入一个新的电压VLL[4]。作为未选中单元的字线电压VLL,被设定为一个绝对值很小的负值,以减小阵列器件的亚阈电流。但是,必须仔细选择一个优化的VLL值,因为采用VLL虽然减小了亚阈区泄漏,但是同时会增加节点结的栅感应漏极泄漏(GIDL)。因此,开始阶段,如期望的那样,通过亚阈行为的改善使泄漏不断减小,但是随着VLL更负,因为GIDL而使泄漏从减小变成不断增大。

选用优化的VBB、VLL和VAA值,可以使阵列器件满足数据保持时间所要求的泄漏标准。最关键的器件参数是阈值电压,它必须被设定到足够大的值。然而,亚阈斜率不会随着几何尺寸缩小。这样,为了保证保持时间,在几代工艺间必须阈值保持相对不变。然而阵列器件的导通电流要求必须支持不断增加的单元读取速度,以减少存取时间。这种情况完全不同于逻辑工艺的情况。对于逻辑工艺,通过工艺缩小获得性能的改善,但是以持续增长的关态泄漏为代价。

对这个问题,最直接的解决方法是采用升高的栅电压VPP。从1980年以来,已经有好几代工艺在DRAM中采用升高的VPP,主要是要求将全部的VAA电平写入存储器单元,这样就要求传送器件的栅电压满足:VPP>(VAA+Vth)。就我们所讨论的关于工艺缩小问题而言,升高的VPP会额外增加读取条件下的驱动电流。因此,当技术边界条件仍然满足时,选择尽可能高的VPP很有优势。

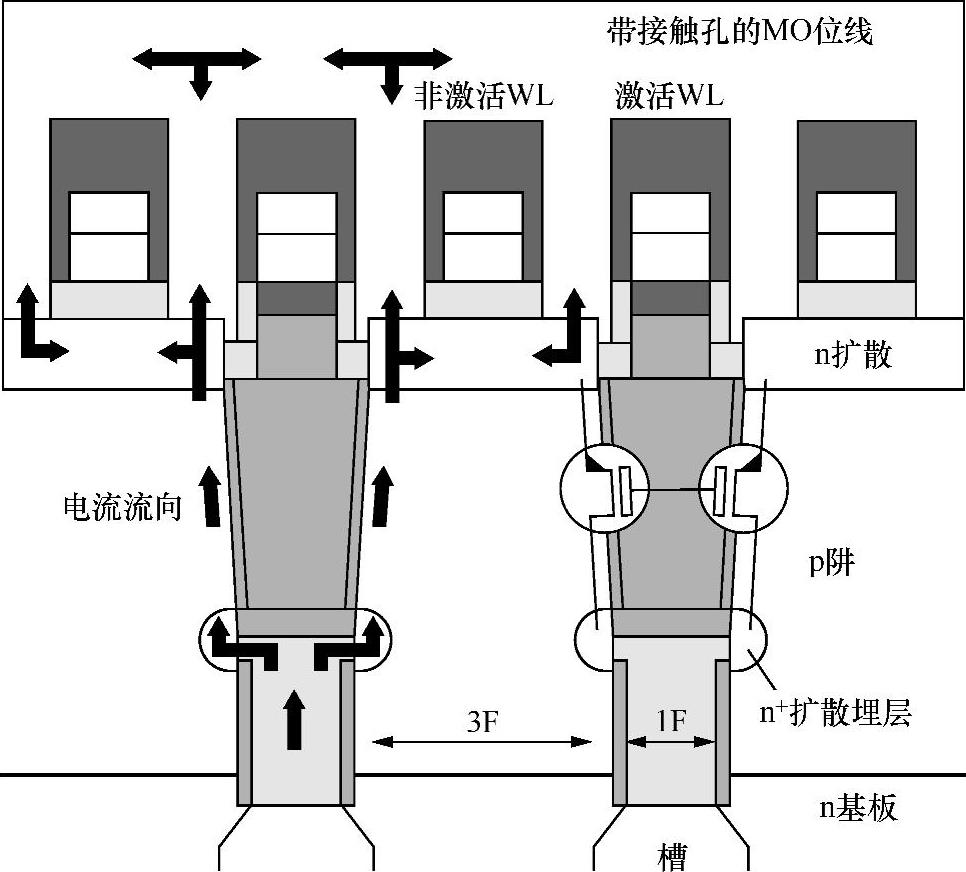

然而,栅氧厚度又设定了一个严格的限制——氧化层中的电场不能超过击穿(GOI)限制,即不能出现介质经时击穿(TDDB),这是一个可靠性问题。虽然击穿电压大于10mV/cm,但是应用中最大电场被限制在约5 mV/cm。为了将这个界限提高,现代的DRAM工艺采用两种栅氧厚度的器件。在外围电路中,器件使用薄栅氧以优化性能,而阵列器件则采用厚氧化层以允许升高的VPP。另外,VPP电荷泵的设计又提出了一个不那么严格的限制。为了使电荷泵的效率高,VPP不能设计得太高。以前,由于电压较高,升高的字线不是太重要。然而,随着将来存储器的外部电源电压快速减小时,在这就变得举足轻重了。下一代器件会工作在1.5V或更低的电压下,上面的描述的原理期望会使能够缩减进入100nm领域。随着尺寸的缩小,在某些情况下,甚至这些办法都会变得不充分了。这样就必须考虑更多的积极方法。通过浏览DRAM电容的历史记录可以获得一种直接的但是在技术上具有挑战性的方案。几代工艺之前,平面的二维电容被三维纵向电容取代。沿着相同的路线,必须探究进一步的革新以继续缩减能进入亚100nm技术。存取晶体管是下一个制约缩减的对象,需要采取创新措施,以克服对缩小的制约。晶体管被垂直折叠进沟槽单元中的实验型DRAM已经证明是可行的[5,6]。这种拓扑结构的优点是阵列器件的沟道长度与目标特征尺寸f无关。图7-8所示为对这一技术的说明。晶体管不再是一个平面器件,而是沿着垂直方向位于硅表面的位线接触扩散与深入到硅内部的沟槽之间。

图7-8 采用垂直存取晶体管的存储器单元(晶体管向垂直方向延伸并实现了与存储器单元电容的三维集成。一个主要优点是存取晶体管的栅长不再与特征尺寸f有关)

虽然存在挑战,人们还是不断产生并实现新的想法,从而在100nm特征尺寸之下继续缩小1T1C单元。如果仔细考虑了电容和存取晶体管,并实现了所有电阻和(耦合)电容的正确建模,建立阵列将不会产生额外的严重问题。下一个挑战是读出放大器的设计。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。