(1)A/D转换的基本概念

A/D转换器的功能是将输入的模拟电压转换为输出的数字信号,即将模拟量转换成与其成比例的数字量。

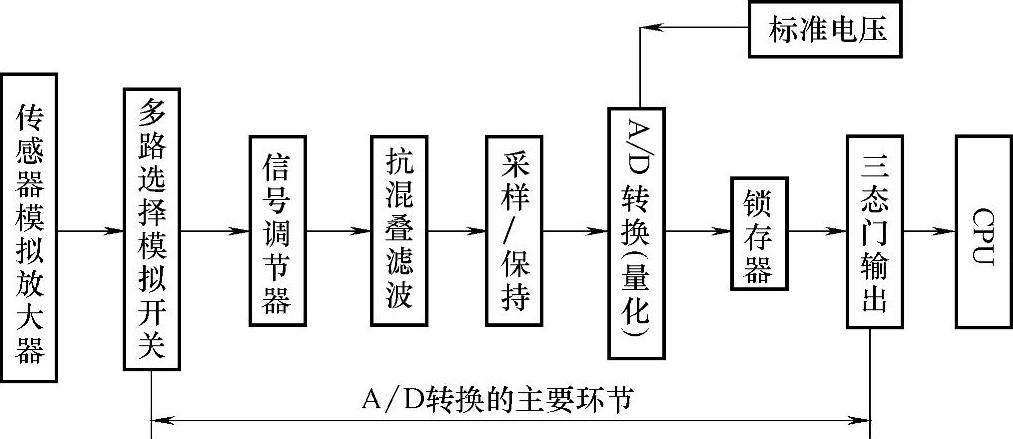

一个完整的A/D转换过程,必须包括采样、保持、量化、编码四部分电路。在具体实施时,常把这四个步骤合并进行。例如,采样和保持是利用同一电路连续完成的。量化和编码是在转换过程中同步实现的,而且所用的时间又与保持的一部分重叠。图7-22是A/D转换的一般过程框图。

图7-22 A/D转换过程框图

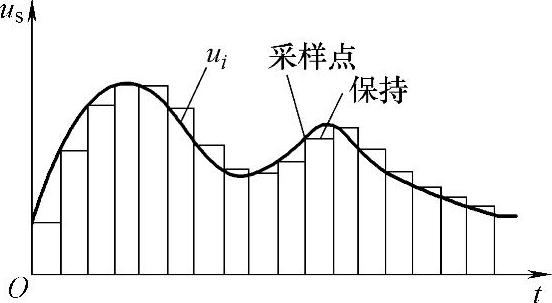

图7-23是某一输入模拟信号经采样后得出的波形。为了保证能从采样信号中将原信号恢复,必须满足条件:

fs≥2fi(max) (7-2)

其中,fs为采样频率,fi(max)为信号ui中最高次谐波分量的频率。式7-2称为采样定理。

A/D转换器工作时的采样频率必须大于等于式7-2所规定的频率,采样的间隔时间决定于A/D转换、采样、通道个数以及程序。采样间隔时间的倒数是采样频率。奈奎斯特采样定理规定:为了使采样输出信号能无失真地复现原输入信号,必须使采样频率至少为输入信号最高有效频率的两倍,否则会出现频率混叠误差。抗混叠滤波的作用是依据采样定理,滤除输入信号过高的频率成分,减小混叠误差。采样频率越高,留给每次进行转换的时间就越短,这就要求A/D转换电路必须具有更高的工作速度。因此,采样频率通常取fs=(3~5)fi(max)即可满足要求。

图7-23 模拟信号采样波形

1)采样/保持电路

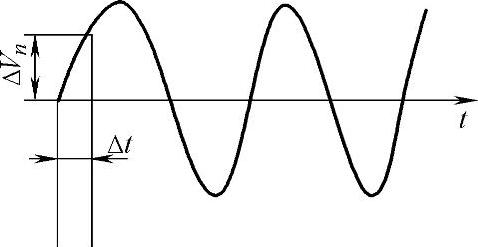

采样/保持的作用是减小孔径误差。模拟量转换成数字量有一个过程,对于一个动态模拟信号,在模/数转换器接通的孔径时间里,输入模拟信号的值是不确定的,从而引起输出的不确定性误差。假设输入信号为一频率为f的正弦信号,如图7-24所示,图中V=Vmsin2πft,由图可明显看出,最大孔径误差一定出现在信号斜率最大处。由数学推导可知,正弦函数的最大斜率是Vm2πf,因此,最大孔径误差是ΔV=Vmsin2πfΔt。对于某个动态信号,其孔径误差与信号的最高频率f和孔径Δt有关。计算表明当10Hz频率信号被采样时,要求在12位分辨率孔径误差小于1/2LSB时,A/D建立时间必须小于2μs。因此采用12位A/D转换器对10Hz或更高频率动态信号采样时,必须使用采样保持电路,以减小孔径误差。比较先进的A/D芯片本身具有采样/保持功能,简化了设计。

图7-24 孔径误差示意图

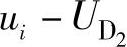

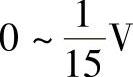

图7-25所示的是一个实际的采样保持电路LF198的电路结构图,图中A1、A2是两个运算放大器,S是模拟开关,L是控制S状态的逻辑单元电路。采样时令uL=1,S随之闭合。A1、A2接成单位增益的电压跟随器,故uo=u′o=ui。同时u′o通过R2对外接电容Ch充电,使uch=ui,因电压跟随器的输出电阻十分小,故对Ch的充电很快结束。当uL=0时,S断开,采样结束,由于uch无放电通路,其电压值基本不变,故使uo得以将采样所得结果保持下来。图中还有一个由二极管D1、D2组成的保护电路。在没有D1和D2的情况下,如果在S再次接通以前ui变化了,则u′o的变化可能很大,以致于使A1的输出进入非线性区,u′o与ui不再保持线性关系,并使开关电路有可能承受过高的电压。接入D1和D2以后,当u′o比uo所保持的电压高出一个二极管的正向压降时,D1将导通,u′o被钳位于 。这里的UD1表示二极管D1的正向导通压降。当u′o比uo低一个二极管的压降时,将u′o钳位于

。这里的UD1表示二极管D1的正向导通压降。当u′o比uo低一个二极管的压降时,将u′o钳位于 。在S接通的情况下,因为u′o≈uo,所以D1和D2都不导通,保护电路不起作用。

。在S接通的情况下,因为u′o≈uo,所以D1和D2都不导通,保护电路不起作用。

2)量化与编码

为了使采样得到的离散的模拟量与n位二进制码的2n个数字量一一对应,还必须将采样后离散的模拟量归并到2n个离散电平中的某一个电平上,这样的一个过程称之为量化。

图7-25 采样保持电路LF198电路结构图

量化后的值再按数制要求进行编码,以作为转换完成后输出的数字代码。量化和编码是所有A/D转换器不可缺少的核心部分之一。

数字信号具有在时间上离散和幅度上断续变化的特点。这就是说,在进行A/D转换时,任何一个被采样的模拟量只能表示成某个规定最小数量单位的整数倍,所取的最小数量单位叫做量化单位,用Δ表示。若数字信号最低有效位用LSB表示,1LSB所代表的数量大小就等于Δ,即模拟量量化后的一个最小分度值。把量化的结果用二进制码,或是其他数制的代码表示出来,称为编码。这些代码就是A/D转换的结果。

既然模拟电压是连续的,那么它就不一定是Δ的整数倍,在数值上只能取接近的整数倍,因而量化过程不可避免地会引入误差。这种误差称为量化误差。

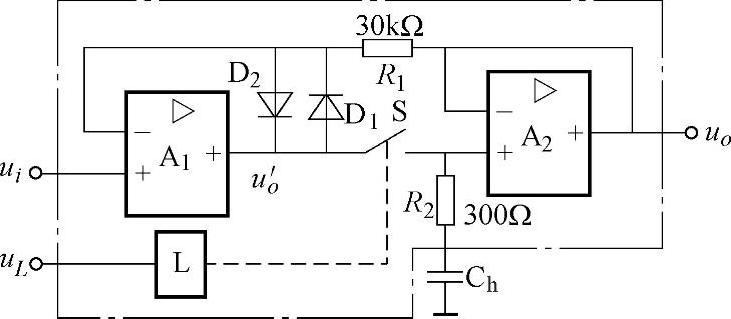

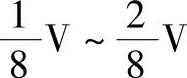

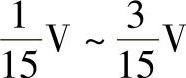

图7-26(a)的量化结果误差较大,例如把0~1V的模拟电压转换成3位二进制代码,取最小量化单位 ,并规定凡数模拟量数值在

,并规定凡数模拟量数值在 之间时,都用0Δ来替代,用二进制数000来表示;凡数值在

之间时,都用0Δ来替代,用二进制数000来表示;凡数值在 之间的模拟电压都用1Δ代替,用二进制数001表示等。这种量化方法带来的最大量化误差可能达到Δ,即

之间的模拟电压都用1Δ代替,用二进制数001表示等。这种量化方法带来的最大量化误差可能达到Δ,即 。若用n位二进制数编码,则所带来的最大量化误差为

。若用n位二进制数编码,则所带来的最大量化误差为 。

。

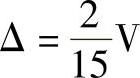

为了减小量化误差,通常采用图7-26(b)所示的改进方法来划分量化电平。在划分量化电平时,基本上是取第一种方法Δ的二分之一,在此取量化单位 。将输出代码000对应的模拟电压范围定为

。将输出代码000对应的模拟电压范围定为 ,即

,即 ;

; 对应的模拟电压用代码用001表示,对应模拟电压中心值为

对应的模拟电压用代码用001表示,对应模拟电压中心值为 ;依此类推。这种量化方法的量化误差可减小到

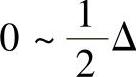

;依此类推。这种量化方法的量化误差可减小到 ,即

,即 。这是因为在划分的各个量化等级时,除第一级(

。这是因为在划分的各个量化等级时,除第一级( )外,每个二进制代码所代表的模拟电压值都归并到它的量化等级所对应的模拟电压的中间值,所以最大量化误差自然不会超过

)外,每个二进制代码所代表的模拟电压值都归并到它的量化等级所对应的模拟电压的中间值,所以最大量化误差自然不会超过 。

。

图7-26 划分量化电平的两种方法

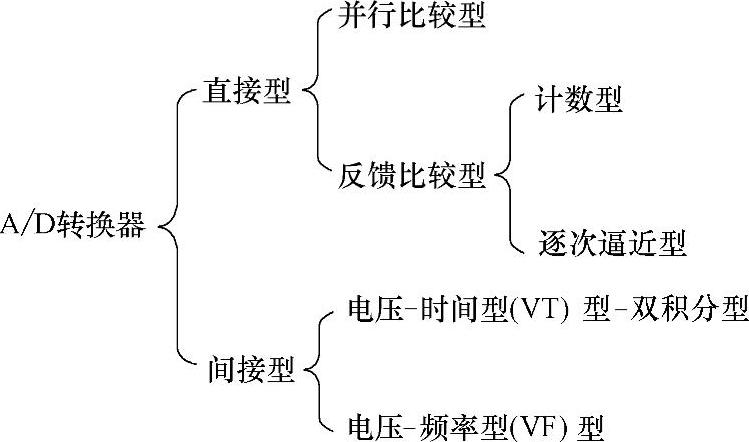

(2)A/D转换器的分类

按转换过程,A/D转换器可大致分为直接型A/D转换器和间接型A/D转换器。直接型A/D转换器能把输入的模拟电压直接转换为输出的数字代码,而不需要经过中间变量。常用的电路有并行比较型和反馈比较型两种。

间接型A/D转换器是把待转换的输入模拟电压先转换为一个中间变量,例如时间T或频率F,然后再对中间变量进行量化编码,得出转换结果。A/D转换器的大致分类如下所示。

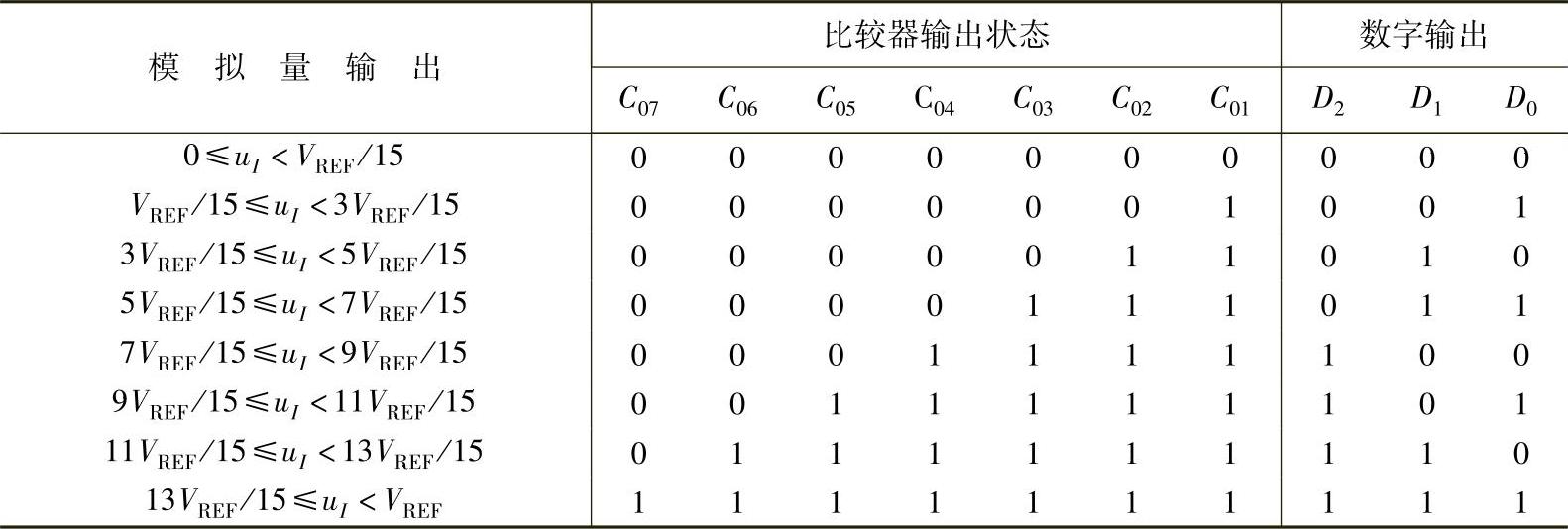

1)并行比较型A/D转换器

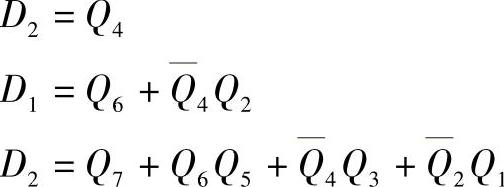

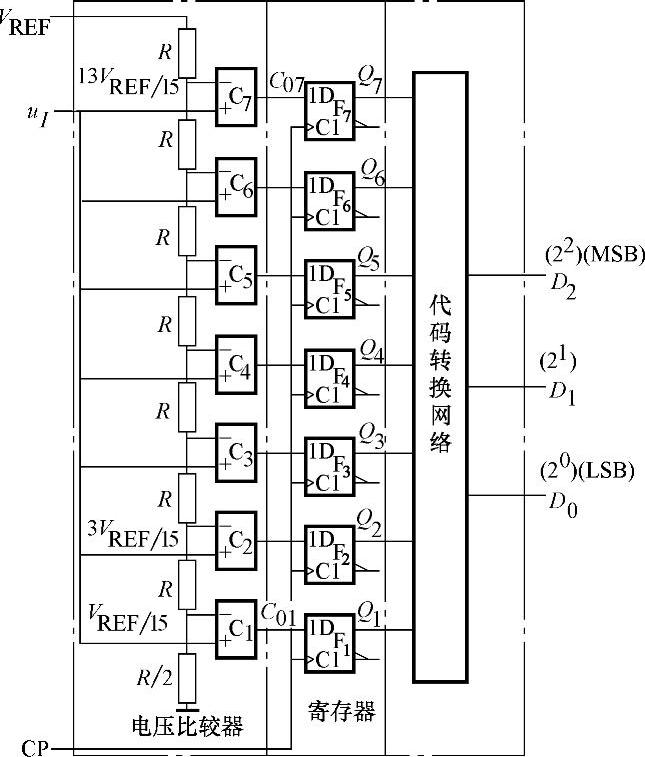

3位并行比较型A/D转换器原理电路如图7-27所示。它由电阻分压器、电压比较器、寄存器及编码器组成。图3-80中的八个电阻将参考电压VREF分成八个等级,其中七个等级的电压分别作为七个比较器C1~C7的参考电压,其数值分别为VREF/15、3VREF/15、13VREF/15。输入电压为uI,它的大小决定各比较器的输出状态,例如,当0≤uI<(VREF/15)时,C1~C7的输出状态都为0;当(3VREF/15)<uI<(5VREF/15)时,比较器C1和C2的输出C01=C02=1,其余各比较器输出状态都为0。根据各比较器的参考电压值,可以确定输入模拟电压值与各比较器输出状态的关系。比较器的输出状态由D触发器存储,CP作用后,触发器的输出状态Q7~Q1与对应的比较器的输出状态C07~C01相同。经代码转换网络(优先编码器)输出数字量D2D1D0。优先编码器优先级别最高是Q7,最低是Q1。

设uI变化范围是0~VREF,输出3位数字量为D2、D1、D0,3位并行比较型A/D转换器的输入、输出关系如表7-11所示。通过观察此表,可确定代码转换网络输出、输入之间的逻辑关系。

图7-27 3位并行比较型A/D转换器原理电路

在并行A/D转换器中,输入电压uI同时加到所有比较器的输出端,从uI加入经比较器、D触发器和编码器的延迟后,可得到稳定的输出。如不考虑上述器件的延迟,可认为输出的数字量是与uI输入时刻同时获得的。并行A/D转换器的优点是转换时间短,可小到几十纳秒,但所用的元器件较多,如一个n位转换器,所用的比较器的个数为2n-1个。

表7-11 3位并行比较型A/D转换器的输入输出关系

单片集成并行比较型A/D转换器产品很多,如AD公司的AD9012(8位)、AD9002(8位)和AD9020(10位)等。

2)逐次逼近型A/D转换器

逐次逼近型A/D转换器属于直接型A/D转换器,它能把输入的模拟电压直接转换为输出的数字代码,而不需要经过中间变量。转换过程相当于一架天平称量物体的过程,不过这里不是加减砝码,而是通过D/A转换器及寄存器加减标准电压,使标准电压值与被转换电压平衡。这些标准电压通常称为电压砝码。

逐次逼近型A/D转换器由比较器、环形分配器、控制门、寄存器与D/A转换器构成。比较的过程首先是取最大的电压砝码,即寄存器最高位为1时的二进制数所对应的D/A转换器输出的模拟电压,将此模拟电压uA与uI进行比较,当uA大于uI时,最高位置0;反之,当uA小于uI时,最高位1保留,再将次高位置1,转换为模拟量与uI进行比较,确定次高位1保留还是去掉。依次类推,直到最后一位比较完毕,寄存器中所存的二进制数即为uI对应的数字量。

3)双积分型A/D转换器

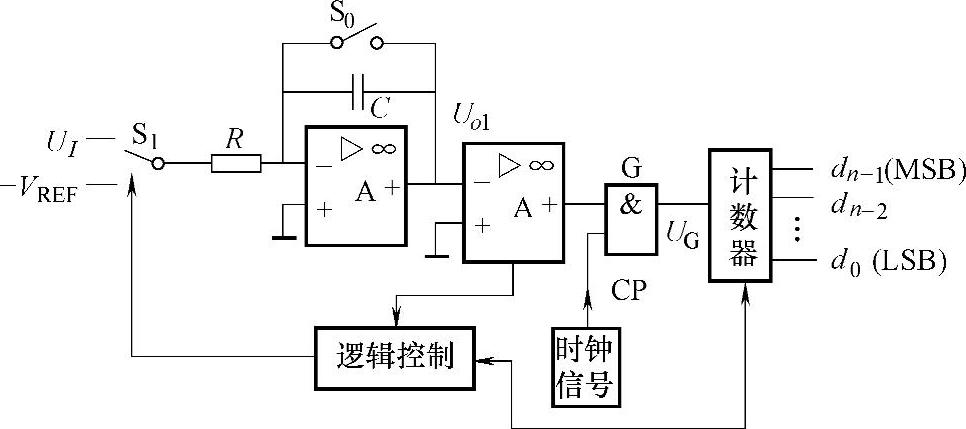

双积分型A/D转换器属于间接型A/D转换器,它是把待转换的输入模拟电压先转换为一个中间变量,例如时间T;然后再对中间变量量化编码,得出转换结果,这种A/D转换器多称为电压-时间变换型(简称VT型)。图7-28给出的是VT型双积分式A/D转换器的原理图。

图7-28 VT型双积分型A/D转换器的原理图

转换开始前,先将计数器清零,并接通S0使电容C完全放电。转换开始,断开S0。整个转换过程分两阶段进行。

第一阶段,令开关S1置于输入信号UI一侧。积分器对UI进行固定时间T1的积分。积分结束时积分器的输出电压为:(https://www.xing528.com)

可见积分器的输出UO1与UI成正比。这一过程称为转换电路对输入模拟电压的采样过程。在采样开始时,逻辑控制电路将计数门打开,计数器计数。当计数器达到满量程N时,计数器由全“1”复“0”,这个时间正好等于固定的积分时间T1。计数器复“0”时,同时给出一个溢出脉冲(即进位脉冲)使控制逻辑电路发出信号,令开关S1转换至参考电压-VREF一侧,采样阶段结束。

第二阶段称为定速率积分过程,将Uo1转换为成比例的时间间隔。采样阶段结束时,一方面因参考电压-VREF的极性与UI相反,积分器向相反方向积分。计数器由0开始计数,经过T2时间,积分器输出电压回升为零,过零比较器输出低电平,关闭计数门,计数器停止计数,同时通过逻辑控制电路使开关S1与uI相接,重复第一步。可得到:

即

式7-4表明,反向积分时间T2与输入模拟电压成正比。

在T2期间计数门G2打开,标准频率为fCP的时钟通过G2,计数器对UG计数,计数结果为D,由于

T1=N1TCP

T2=DTCP

则计数的脉冲数为

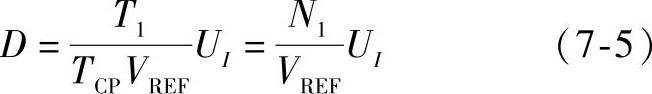

图7-29 双积分型A/D转换器波形图

计数器中的数值就是A/D转换器转换后的数字量,至此即完成了VT转换。若输入电压UI1<UI,U′O1<UO1,则T′2<T2,它们之间也都满足固定的比例关系,如图7-29所示。

双积分型A/D转换器若与逐次逼近型A/D转换器相比较,因有积分器的存在,积分器的输出只对输入信号的平均值有所响应,所以,它突出优点是工作性能比较稳定且抗干扰能力强。由以上分析可以看出,只要两次积分过程中积分器的时间常数相等,计数器的计数结果与RC无关,所以,该电路对RC精度的要求不高,而且电路的结构也比较简单。双积分型A/D转换器属于低速型A/D转换器,一次转换时间为1~2ms,而逐次比较型A/D转换器可达到1μs。不过在工业控制系统的许多场合中,毫秒级的转换时间已经绰绰有余,双积分型A/D转换器的优点正好有了用武之地。

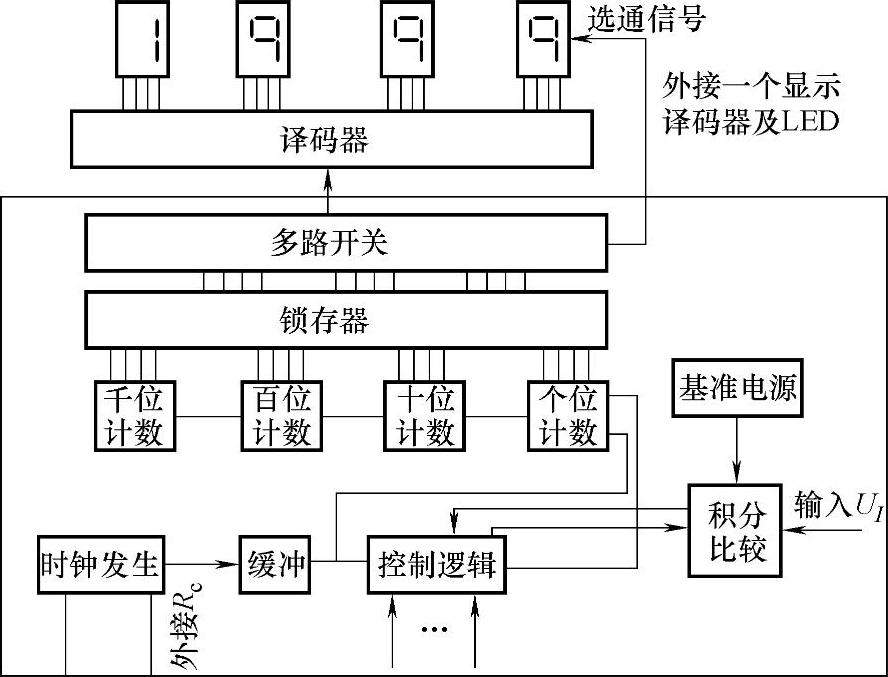

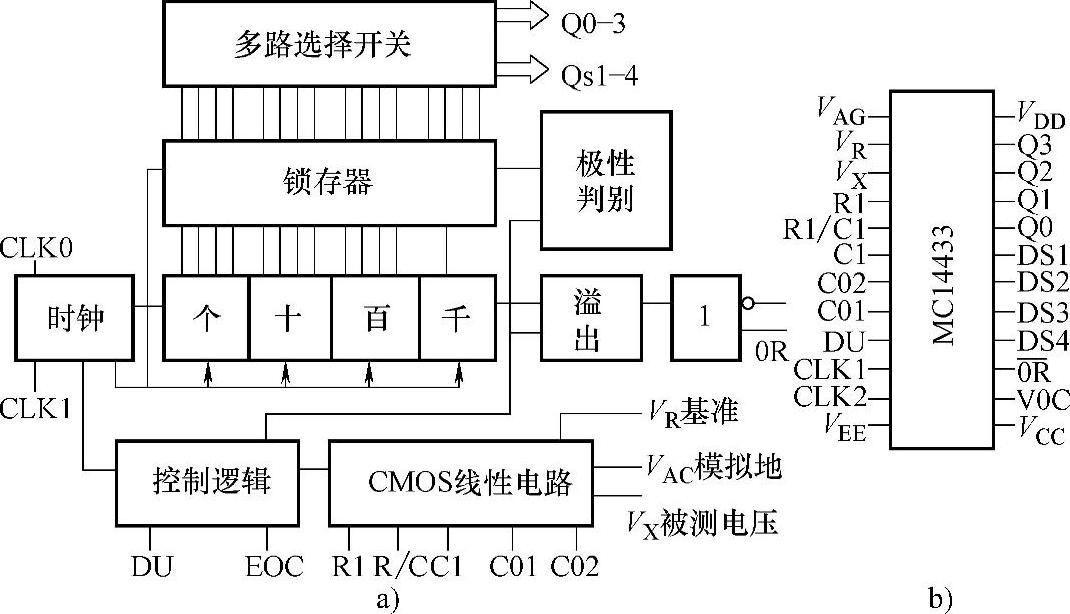

图7-30 BCD码双积分型A/D转换器的框图

集成双积分型ADC品种有很多,大致分成二进制输出和BCD输出两大类,图7-30是BCD码双积分型A/D转换器的框图,它是一种 位BCD码A/D转换器。这一芯片输出数码的最高位(千位)仅为0或1,其余3位均由0~9组成,故称为

位BCD码A/D转换器。这一芯片输出数码的最高位(千位)仅为0或1,其余3位均由0~9组成,故称为 位。

位。 位的3表示完整的三个数位有十进制数码0~9,

位的3表示完整的三个数位有十进制数码0~9, 的分母2表示最高位只有0、1二个数码,分子1表示最高位显示的数码最大为1,显示的数值范围为0000~1999。同类产品有ICL7107、7109、5G14433等。双积分型A/D转换器一般外接配套的LED显示器件或LCD显示器件,可以将模拟电压uI用数字量直接显示出来。

的分母2表示最高位只有0、1二个数码,分子1表示最高位显示的数码最大为1,显示的数值范围为0000~1999。同类产品有ICL7107、7109、5G14433等。双积分型A/D转换器一般外接配套的LED显示器件或LCD显示器件,可以将模拟电压uI用数字量直接显示出来。

为了减少输出线,译码显示部分采用动态扫描的方式,按着时间顺序依次驱动显示器件,利用位选通信号及人眼的视觉暂留效应,就可将模拟量对应的数字量显示出来。

这种双积分型A/D转换器的优点包括:利用较少的的元器件就可以实现较高的精度(如 位折合11位二进制);一般输入都是直流或缓慢变化的直流量,抗干扰性能很强。广泛用于各种数字测量仪表,工业控制柜面板表,汽车仪表等方面。

位折合11位二进制);一般输入都是直流或缓慢变化的直流量,抗干扰性能很强。广泛用于各种数字测量仪表,工业控制柜面板表,汽车仪表等方面。

(3)常用A/D转换芯片

A/D转换芯片种类繁多,接口方法各有特点,这里重点介绍A/D芯片的外特性及与单片机的接口方法。

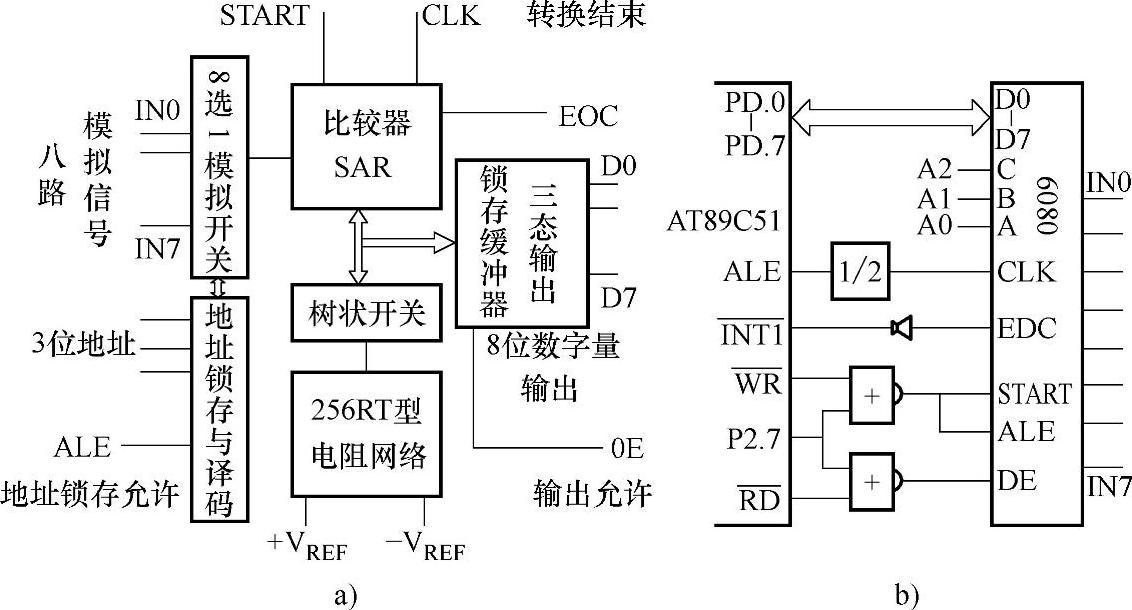

1)ADC0809的接口电路

ADC0809的工作原理、引脚功能、与微处理器AT89C51的接口电路如图7-19所示。

CPU对ADC0809的控制原理如下:由图7-31可以看出ADC0809通过模拟开关接8路模拟信号;74LS138译码器的三条地址选择线A、B、C与地址线A0、A1、A2连接(实际接74LS373的Q1、Q2、Q3),ALE在上升沿时把地址信号锁存起来,地址信号控制模拟开关选中哪一路模拟信号。

电阻网络、树状开关、外接标准电源、比较器、逐次比较寄存器SAR及时钟信号组成8位A/D转换电路,-VREF和+VREF是基准参考电压,它决定了输入模拟量的量程范围。在一般情况下,+VREF与VCC相连,-VREF与地相连。如果需要高精度的参考电源或为了提高转换器的灵敏度(输入模拟电压小于5V),则参考电压可以与VCC隔离。START在正脉冲时启动A/D转换,100μs后转换结束,结果存放于锁存缓冲器。三态输出锁存缓冲器的8条输出信号线D0~D7直接与CPU的数据总线连接。OE(OUTPUTENABLE)端为允许输出控制端,CPU使该控制端为高电平“1”时,三态门打开,A/D转换的结果送入CPU。A/D转换结束时,EOC出现高电平。人们可以用它引起中断,也可做查询用。

图7-31 ADC0809引脚及接口电路

a)引脚图 b)接口电路

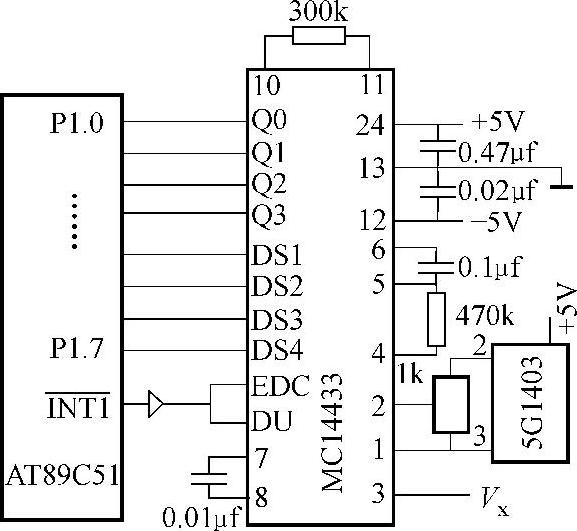

2)MC14433的接口设计

MC14433是 位双积分式A/D转换器。图7-32是该芯片的引脚分布。图7-33是MC14433的接口电路。

位双积分式A/D转换器。图7-32是该芯片的引脚分布。图7-33是MC14433的接口电路。

图7-32 MC14433引脚分布

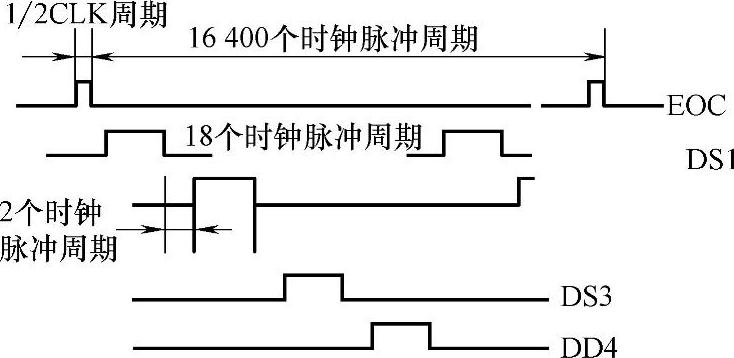

图7-34示出了MC14433的转换结果输出时序波形。从图中可以看出,转换结果的千位值、百位值、十位值、个位值是在DS1-DS4的同步下分时由Q3~Q0送出的。

图7-33 MC14433的接口电路

图7-34 MC14433转换结果输出时序波形

(4)A/D转换器的性能指标

1)转换精度

在单片A/D转换器中,也用分辨率和转换误差来描述转换精度。分辨率是指引起输出二进制数字量最低有效位变动一个数码时,输入模拟量的最小变化量。小于此最小变化量的输入模拟电压,将不会引起输出数字量的变化。也就是说,A/D转换器的分辨率,实际上反映了它对输入模拟量微小变化的分辨能力。显然,它与输出的二进制数的位数有关,输出二进制数的位数越多,分辨率越小,分辨能力越高。但若超出了A/D转换器分辨率的极限值,再增加位数,也不会提高分辨率。

A/D转换器的分辨率习惯上以输出二进制位数或者BCD码位数表示。与一般测量仪表的分辨率表达方式不同,不采用可分辨的输入模拟电压相对值表示。例如AD574A的分辨率为12位,即该转换器的输出可以用212个二进制数进行量化,其分辨率为1LSB(LSB指最低有效位)。如果用百分数来表示分辨率时,其分辨率为:

1/212×100%=1/4096×100%=0.0244%

5G14433双积分式A/D转换器为BCD码输出,其分辨率为 ,满度字位为1999,用百分数表示其分辨率为(1/1999)×100%≈0.05%。

,满度字位为1999,用百分数表示其分辨率为(1/1999)×100%≈0.05%。

量化误差和分辨率是统一的,量化误差是由于有限数字对模拟数值进行离散取值(量化)而引起的误差。理论上量化误差为一个单位分辨率,即±1/2LSB。

转换误差通常以相对误差的形式给出,它表示A/D转换器实际输出的数字量与理想输出的数字量之间的差别,并用最低有效位LSB的倍数来表示,提高分辨率可以减少量化误差。

2)转换时间

转换时间表示完成一次从模拟量到数字量之间的转换所需要的时间,其倒数为转换速率。它反映了A/D转换器的转换速度。目前,转换时间最短的是全并行式A/D转换器,例如美国RCA公司生产的TDC1029J,其分辨率为6位,转换速率为100MSPS,转换时间为10ns。逐次比较式A/D转换器的转换时间可达0.4μs;双积分A/D转换器的转换时间一般为40~50ms。

采样定理和减小孔径误差都要求转换时间越小越好,转换速率越快越好。但目前速度最快的全并行式A/D转换器价格比较贵,且分辨率低。双积分式A/D转换器速度慢,但价格便宜,抗干扰能力强。逐次比较式A/D转换器的速度和价格居中,分辨率远高于并行式A/D转换器,它是目前种类最多、数量最大、应用最广的A/D转换器。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。