集成芯片器件有效运行的主要要求之一是要维持供电干线(电路供电电压干线和电路接地电压干线)上电压水平的稳定。供电干线上电压水平的变化会改变漏极-源极电压和触发电压。供电干线上的电压太低,会降低漏极电压和触发电压,因而可能导致晶体管错误开关,从而造成整个电路的运行失效。理论上,提高供电干线上的供电电压是减少低电压相关问题的方法。但是,输入电压提高会增加器件的功耗,并会对晶体管的可靠性造成很大影响。对输送稳定电压的要求,已促使功率传输管理成为电子封装领域的一门主要学科,尤其在微处理器等高性能逻辑器件的封装上。

微处理器的功率输送所面临的挑战可以分成如下所述的三个方面:

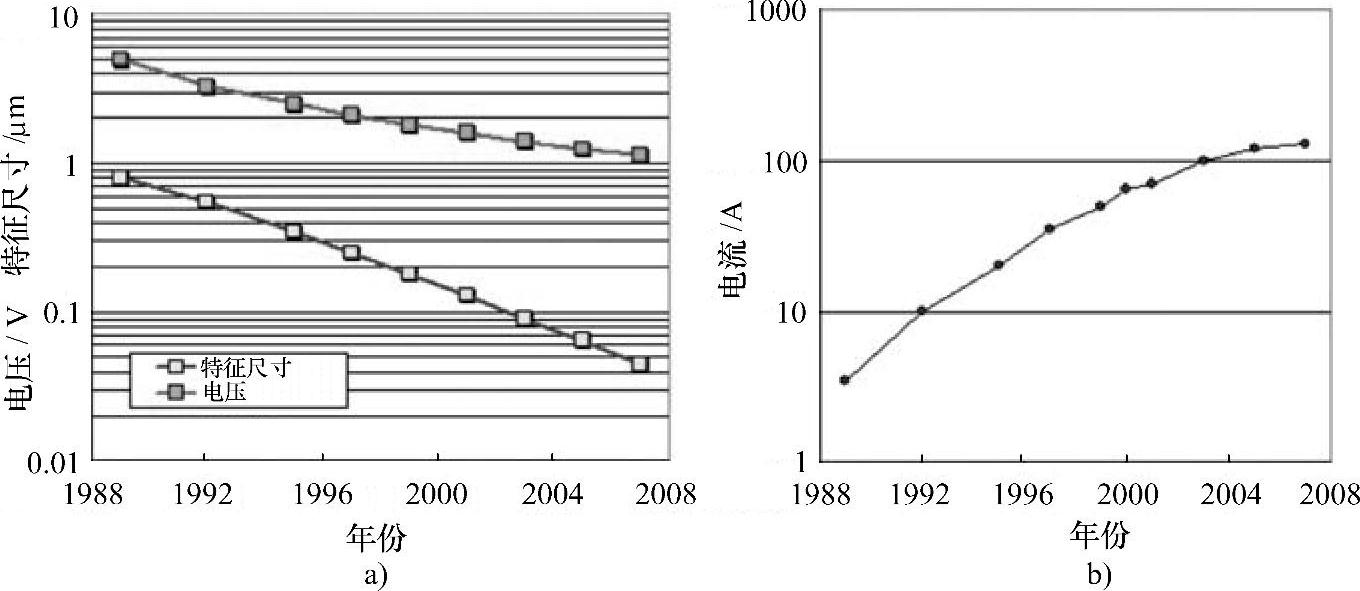

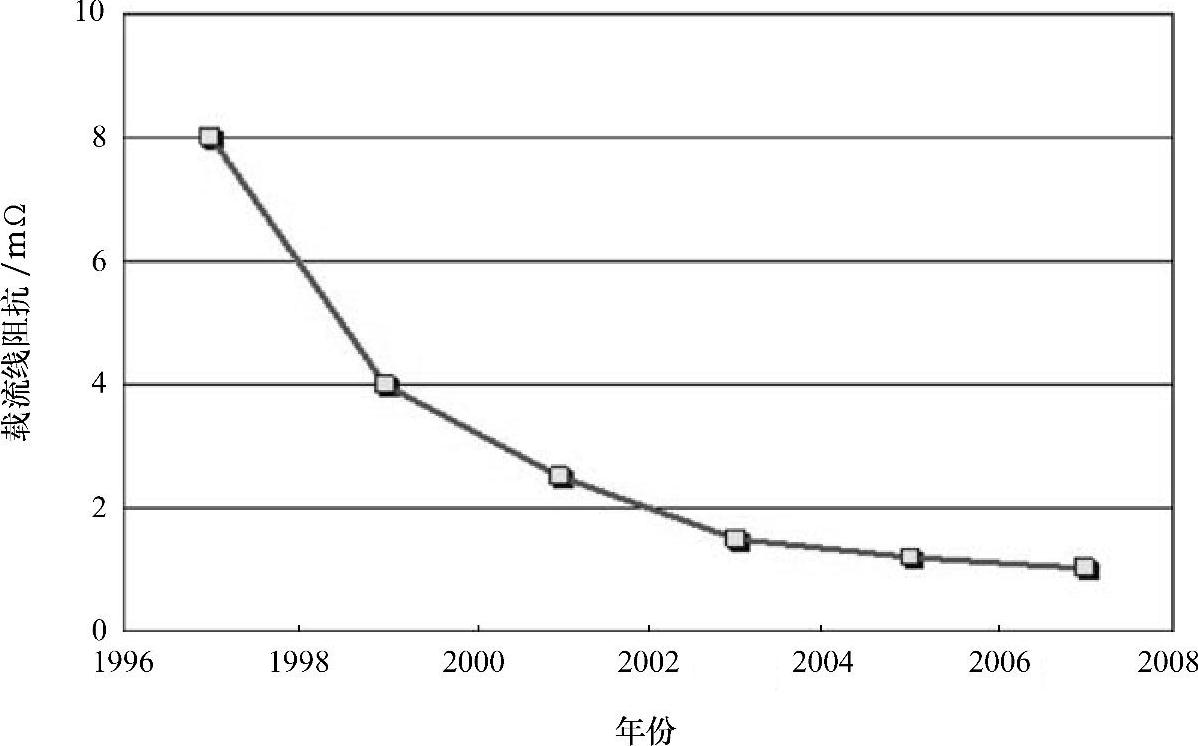

(1)随着晶体管特征尺寸的减小,微处理器的运行电压持续下降,如图22.10a所示,以便维持晶体管的可靠性并最小化功率消耗。因为在设计微处理器时利用了硅尺寸和速度上的进步来改善微处理器的性能,使微处理器芯片中的电流不断增加,尽管其增加的速率呈正在下降的趋势,如图22.10b所示。这些趋势的总体影响是功率传输线路上的目标阻抗,即供电电压与供电电流的比,继续减小,如图22.11所示。

图22.10 美国英特尔公司微处理器选通脉冲宽度、电压和电流的发展趋势

a)随着晶体管特征尺寸减小微处理器的运行电压持续下降 b)微处理器芯片中电流的增加

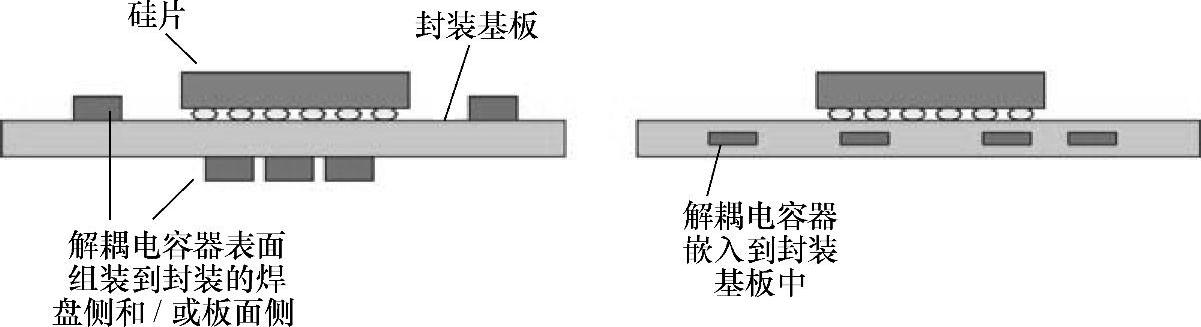

(2)在典型微处理器应用中,电源供应的实际电流(power supply current draw)能够突变,因此功率输送网络必须能够快速反应、提供电荷,否则供电电压可能低于所需的最低值。这意味着设计功率输送网络时,必须保证功率输送网络能匹配各种频率源电流下的目标阻抗值,源电流可为直流,甚至是几百兆赫兹的交流。这个任务是通过设计一个多级解耦器完成的。在解耦器中,用于高频应用的电容安装在封装上(见图22.12),用于中频应用的电容安装在靠近封装的母板上,用于低频应用的电容器则安装在母板上电压调节器输出端[13]。

(3)器件尺寸减小的不利之一是晶体管耗散功率[13]的增加。为了在有限的功率预算下持续提供更多的功能,微处理器正在由单芯结构向多芯结构转变[14]。另外,使用低功耗的休眠状态也使得芯片设计人员能够减小功耗。要完成这些结构转变则需要仔细地设计功率传输网络,以此来保证每个微处理器在不同的操作状态时各个处理器芯的功率输送线路阻抗是最小的。(https://www.xing528.com)

图22.11 英特尔微处理器功率输送目标阻抗(载流线)的发展趋势

图22.12 高频解耦技术

微处理器封装中的高频解耦电容技术已经从简单的二极(Two-Terminal,2T)电容发展成复杂的叉指型电容(Interdigitated Capacitor,IDC)[13]。IDC因自身有许多低电感电流通路,从而减小了供电电压端Vcc和接地电压端Vss之间的有效回路电感。这些低电感电流通路是Vcc和Vss端布局创新的结果。因此,相比2T电容,IDC能更有效地减小高频干扰。电容电感更进一步地减小可以通过电容阵列技术实现。在电容阵列技术中,电容的表面有接触引脚面阵,且电容被连接至多个导电电镀孔。需要注意的是,任何类型电容的高频解耦性能都能通过把许多电容并联使用来提高。但是,在电容类型和大量低性能电容之间进行选择时,需要考虑到电容器附属物的可用封装表面和解耦的总成本。

因为电容的电感值减小,电容和微处理器之间导电线路的电感就成为下一个主要挑战。封装中功率输送线路高频负载线的效果管理上,电容连接到芯片的方法扮演了重要的角色。例如,与设置在管芯侧的电容相比,放置在封装焊盘侧(pack-age landside)直接在管芯下面的电容能更快地向芯片传输功率,因此其功率提供性能也更好。通过把分立的或组合的电容嵌入在封装基板中,并且使其最接近管芯上分散的高负荷区域,可以进一步提高电容的功率传输性能(见图22.12右图)。实现电容的嵌入则需要电容、主板材料和加工工艺的改进[15]。

通过减小母板电压调节器和微处理器芯片间功率传输线路的直流电阻,可以控制低频阻抗。典型的方法有减小插孔的电阻、增加封装上电源组和接地针的数量,以及增加电源组和地线层铜板的厚度。为了抑制因管针数目增加而造成的封装尺寸增加(和由此带来的成本增加),插孔管针的尺寸也随着时间减小。但实际上,减小插孔间距和增加管针数目会受到限制,因此需要探索新的设计思路,比如分离出电压调节器的功率线路并使之更接近管芯。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。