RC分析最适合应用于局部层和中间层的电阻性网络,电感效应经常表现在较宽的全局互连中。全局互连用于在功能块之间传输信号、分布时钟参考、为逻辑门供电。为了在高性能电路中能合理地设计这些互连,需要采用表征信号传输特性的RLC模型和技术。然而,由于以下两个原因,电感效应增加了时序和噪声分析的复杂度。首先,不像容性耦合那样只受最邻近互连的影响,感性耦合的影响会扩展到更远的范围。与电场的行为不一样,磁场在金属表面是非零的,因此互感随着距离衰减得非常慢。其次,因为片上互连结构没有提供意义明确的直流路径以构成电路回路,电路中感性电流返回路径存在不确定性。因此,RLC分析不是局部问题,这意味着必须在较大范围内考虑足够多的相邻互连才能得到正确解。另外,对主要的性能度量,获得简单的解析解也非常困难,因为如式(8.2.3)所示,电感引起的是非单调行为(如振铃和过冲),所以需要匹配更多的矩才能逼近输出特性。

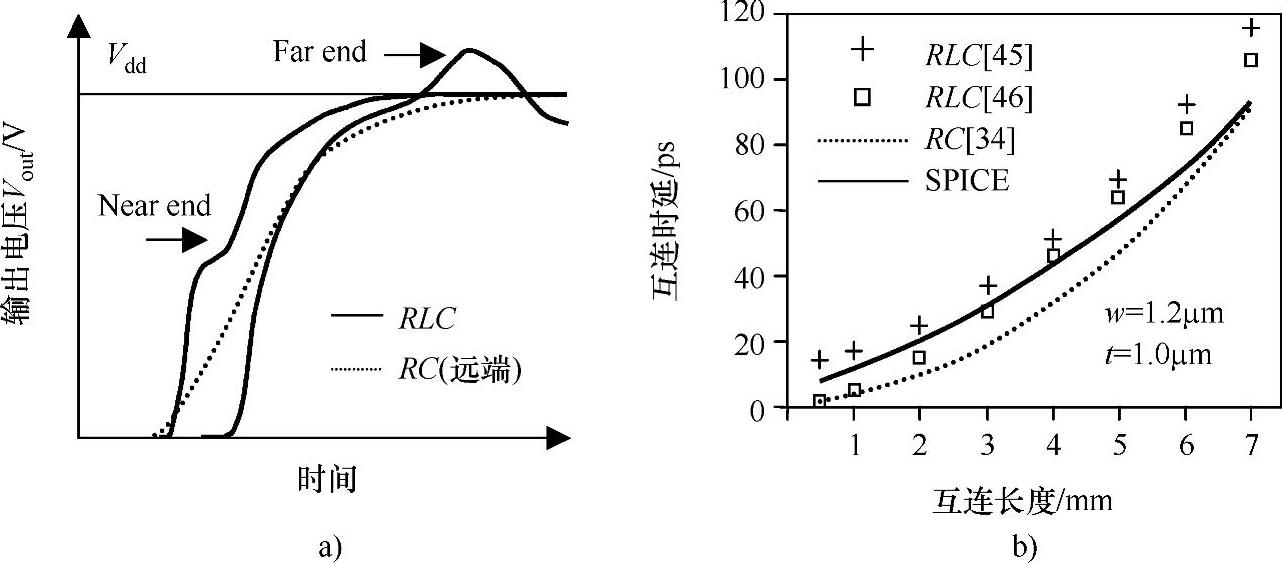

RLC互连时序分析 与RC互连相比,RLC互连在电压开关的传输过程中表现完全不同,具有更大的时延、更快的压摆率、有振铃也有过冲。图8-12a是180nm工艺中电感对典型全局互连上斜坡响应波形的影响。由于感性阻抗的作用,50%Vdd增加,而对时钟边沿和串扰噪声特别重要的信号压摆率则减小了。估计这个效应时,必须考虑两个因素:一方面,一个更陡峭的信号边沿对数字设计更有益,因为状态跳变只需更短的时间;另一方面,信号开关越快,串扰噪声越大(源自容性和感性耦合)。因此,一个最佳的设计应该在给定的噪声约束下实现最小的压摆率。在RLC中存在有电压振铃和过冲,而在RC互连中则没有,这是具有感性元件的传输线行为所造成的。这些不期望的特性可能进一步引起不期望的后果:振铃影响时钟信号的稳定,因为较大的振铃会被错误地当作是一次跳变,从而引起逻辑错误;而电压过冲可能增加功耗并使栅氧甚至整个器件的可靠性退化。除了在RLC互连的远端存在波形特性外,在沿互连的其他各点上也会出现不期望的行为。例如,图8-12a还给出了互连近端的情况,如果驱动器和互连的阻抗不匹配,则电压波形在跳变边沿的中部会出现一个平台。在阈值附近出现这样的电压平台将可能加大驱动器时延,但是这个效应可以通过驱动器尺寸的调整得到优化。

图8-12 开关行为的比较

a)输出波形比较 b)时延预测比较

与RC互连分析相似,RLC时序分析可以使用一般的数值技术[27,45]或者解析方法。解析方法的高效率非常适合于全局的RLC互连布线和优化。为了简化建模时感性耦合的复杂度,首先用等效回路电感Lloop的概念对目标互连与其相邻互连进行去耦。对屏蔽良好的结构,例如时钟线,Lloop可以通过计算给出解析解[25,26]。而对于多位的数据总线结构,很容易建立一个可供查阅的查找表,其中Lloop的值是互连配置和输入开关模式的函数[24]。计算获得Lloop的值之后,单个RLC互连的输出波形可以用矩匹配技术求解[30,46,47],并且时延度量可以近似为

式中,ζ和ωn是互连寄生参数的函数[46]。类似的结果还可以参见参考文献[47]和[48]。注意,当4L/R2C>1时(R、L、C是整个互连长度上总的线寄生参数),会发生信号的振铃和过冲。基于解析时延度量,图8-12b比较了由各种RC和RLC模型预测的互连时延。总之,考虑到电感影响,信号时延增加了约15%,并且在互连长度为2~5mm范围,RLC模型与SPICE结果非常吻合[8]。

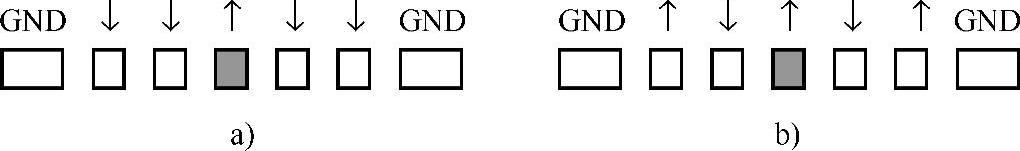

除了互连本身的特性外,当邻近的互连都有开关动作时,信号的时延还与多位数据总线的输入向量有关。为了设计一个能查找潜在的信号完整性问题的验证工具,了解攻击线在最坏情况下的开关方向是非常重要的。如果采用简单的RC模型,业已明确,当受害线开关模式的方向与其相邻互连完全相反时,它将承受最大的有效耦合电容,从而产生最坏的时延情况。考虑长距感性耦合时,对最坏情况估计必须给出全部输入开关模式。如图8-13所示,最坏输入向量的两种情况都是对称的。第一种情况(见图8-13b)对应于所有的邻近邻线同向开关,而且与目标互连方向相反。如果互连以RC为主,则时延最大。如果更远的互连与目标互连同向开关,因为同相开关产生了最大的回路电感,则电感效应占主导地位(见图8-13b)对应于导致最坏时延的第二种输入模式。在180nm节点,第二种输入模式代表了许多电路实例中的最坏情况[24]。但是,实际中最坏情况的开关模式不仅与RLC参数有关,还取决于工艺。

图8-13 最坏情况可能的输入向量(箭头↑表示向上开关;箭头↓表示向下开关)(https://www.xing528.com)

a)模式1:容性耦合为主 b)模式2:感性耦合为主

总之,只要输入向量合适,RLC模型会给出信号时延估计的一个上限,而RC模型一般会给出压摆率计算的一个下限。

感性耦合噪声 工作频率和全局互连长度的持续增加不仅会导致显著的电感效应;而且会加重纳米领域的串扰噪声。在容性串扰和感性串扰之间,存在两点基本差异:

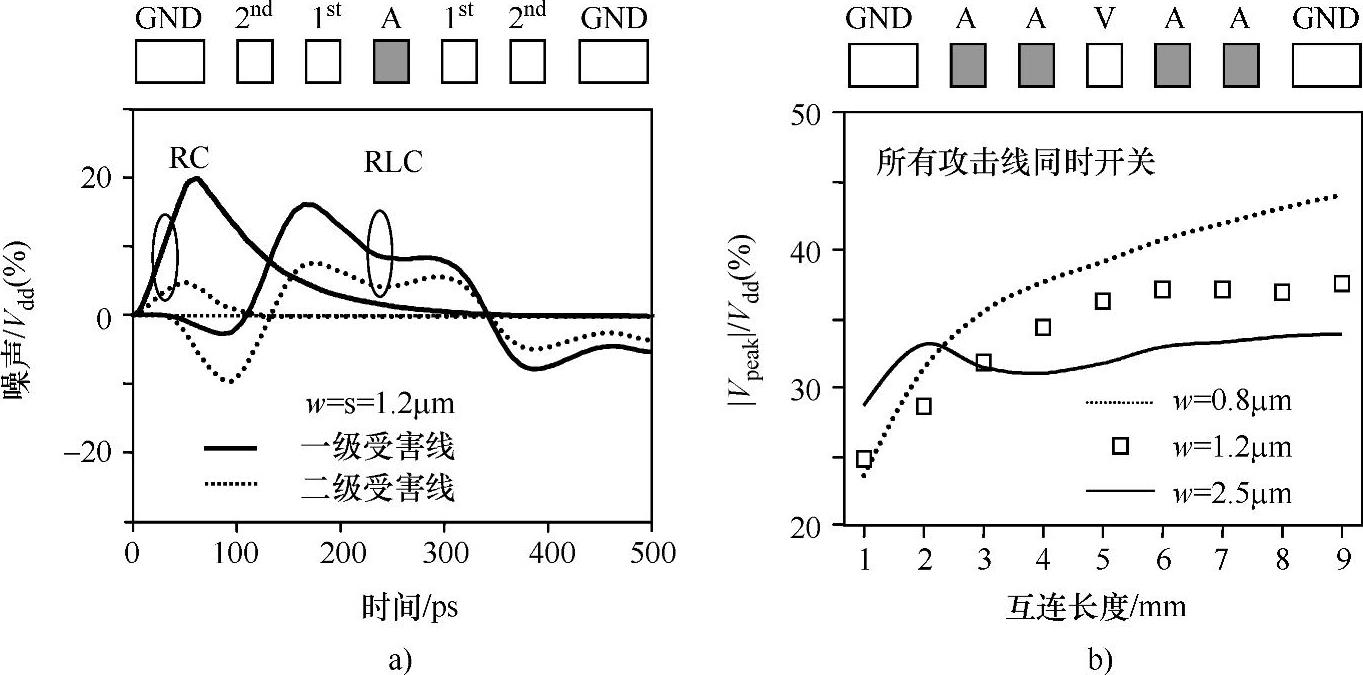

(1)噪声的极性。在容性耦合中,串扰噪声(C(dV/dt))的方向总是与“攻击线”开关的方向相同。然而,感性耦合通过返回电流产生的噪声(L(dI/dt)),则与攻击线开关的方向相反,并且发生的比C(dV/dt)更及时。因此,对于给定的攻击线开关动作,感性噪声的极性一般与容性耦合的极性相反并且出现的时间更早,如图8-14a所示。对第一阶和第二阶邻线,正的(即容性耦合)和负的(即感性耦合)噪声峰值都与RLC预测结果比较吻合。然而,这些相反的因素抑制着相邻互连间耦合噪声的幅度。

(2)耦合范围。因为感性耦合产生的返回电流延伸的距离和范围很广,即使更高阶的受害线也可能受到RLC串扰噪声的影响,如图8-14a所示。虽然容性耦合随着距离的增加快速衰减,而对于非相邻互连之间的感性耦合却不能忽略。实际上,由于第二阶互连上没有相反的容性耦合噪声,使得第二阶互连的最大感性噪声(负的峰值)会大于第一阶互连的感性噪声。

由于这些耦合机制的竞争特性,没有电路仿真器的辅助很难精确预测总的RLC串扰噪声行为。图8-14b显示了峰值噪声和互连长度之间的复杂关系。较宽互连的Vpeak值更趋向于感性效应,并且表现出非单调的相关性;在RC占主导的较窄互连中,Vpeak值随着长度的增加而单调增加。另外,特别是在较长的平行数据总线结构下,感性耦合噪声比容性耦合噪声更严重且更难控制。实际应用中,为了限制返回电流,在每两根或每四根信号线之间插入回路电源线和地线。然而,即使采用这种预防性的方式,感性噪声仍然会跨过屏蔽区对受害线产生影响[49]。因此,应该在设计的早期阶段就采用版图(比如参考文献[50]中的内容)或电路设计技术预防电感效应的影响,而不是依靠在后期验证阶段的昂贵分析工具。

图8-14 180nm铜互连工艺(互连长度=3mm;A代表“攻击线”;

V代表受害线的串扰噪声比较

a)噪声波形比较 b)不同宽度的峰值比较

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。