芯片的可靠性内容较多,其中最基本的两个是闩锁效应和静电效应。

1.闩锁效应(latch up)

硅栅CMOS中的闩锁效应起因于寄生NPN和PNP双极晶体管形成的PNPN结构(即寄生晶闸管)。闩锁效应很容易发生,特别是在芯片的输入、输出端,因为芯片的输入、输出端多数是由大尺寸的数字反相器组成的输入、输出缓冲器,并且通常有大的输出驱动电流,如图3-18所示的大驱动管,因此最容易出现闩锁效应。实际上,如果电压上升到高于VDD或下降到低于VSS,也容易产生寄生晶闸管效应,由于输入、输出压焊块是和外部电路接口的,所以最容易出现上述情况。另外,任何不与衬底、电源连接的引脚引线也都有可能发生。

解决闩锁效应最有效的方法是加保护环,并且如果有可能,尽量用双重保护环,比如对输出MOS(即漏区直接接到外部电路元器件上的MOS管)最好采用这种保护措施,以避免闩锁效应,即NMOS管由连接到VSS的P+环和连接到N阱中的N+环包围;PMOS管由接到VDD的P+环和连接到衬底的N+环包围,另外一定要保证这些环的有源区应该是连续的。

2.静电效应

(1)静电现象简介

静电是一种电能,它存在于物体表面,是正负电荷在局部失衡时产生的一种现象。当带了静电的物体跟其他物体接触时,这两个具有不同静电电位的物体依据电荷中和的原则就会存在电荷流动,传送足够的电量以抵消电压差。在这种高速电量的传送过程中将产生潜在的破坏电压、电流以及电磁场,严重时会将物体击毁,这就是静电放电,也称为ESD(ElectroStatic Discharge)。

ESD是当今MOS集成电路中最重要的可靠性问题之一。高密度集成电路器件具有线间距短、线细、集成度高、运输速度快、低功率和输入阻抗高的特点,因而导致这类器件对静电较敏感,称为静电敏感器件。静电放电的能量对传统的电子元件的影响甚微,人们不易觉察,但是这些高密度集成电路元件则可能因静电电场和静电放电电流引起失效,或者造成难以被人们发现的“软击穿”现象,导致设备锁死、复位、数据丢失和不可靠,影响设备正常工作,使设备可靠性降低,甚至造成设备的损坏。D508项目内置了一路高灵敏度的输入端,可以感应外部电容的改变来调整内部的检测振荡器的频率,从而实现感应触发。这种感应是通过人体手指靠近芯片所引出的感应端而实现的,而人体是最大的静电携带者,因此这类电路非常容易受到ESD的影响而导致功能失效。

(2)ESD的测试模式

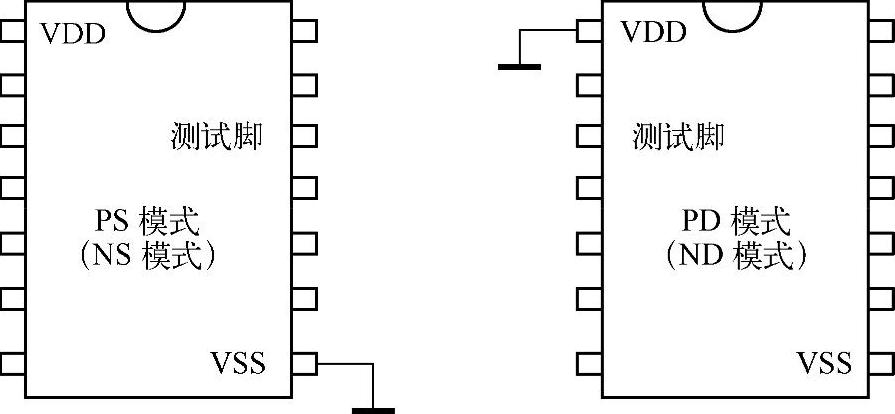

对于芯片的每个端口,都有4种ESD的测试模式,分别是对±VDD和±VSS模式进行测试(分别称为PS模式ALL TO VDD+、NS模式ALL TO VDD-、PD模式ALL TO VSS+和ND模式ALL TO VSS-),如图3-21所示,针对其中某一个测试脚,施加正的或者负的ESD电压,其余不测的端口全部悬空,只有当4种模式全部成功通过某一电压(如4000V)测试,才能认为此端口的抗ESD能力达到了4000V。

ESD测试中用得较多的是人体模型工业测试标准HBM MIL-STD-883F3.15.7。以PS模式为例具体说明测试方法:每种电路准备3个样品,这3个样品首先必须通过功能的测试;电源引脚悬空,接地引脚接低电平,其他所有引脚也都浮悬空,在某一个测试引脚上施加正电压来等效实际电路使用时所承受的正的ESD电压,起始电压为500V,以后每做一次测试电压往上增加500V,也就是说步进电压为500V;然后监控该测试引脚在施加ESD电压前后的电流-电压曲线,通常采用包络线法来判断施加ESD电压前后测试引脚的电流-电压曲线的变化。当相对包络线小于15%的变化判断为施加ESD电压前后的电流-电压曲线没有变化,该引脚还可以承受更高的ESD电压。继续往上增加电压,直到超出15%这个范围,比如加到4500V,相对包络线超出了15%的变化,就表明该测试引脚已经超过了ESD承受范围,而这个时候所加的ESD电压4500V的前一档,也就是说,4000V就是该测试引脚所能承受的最高ESD电压;然后再对该测试引脚进行NS、PD、ND等其他3种模式的测试,如果4种模式都能通过4000V,并且经过ESD打击后电路的功能没有改变,还要3个样品都能够重复该试验,这才表示这个引脚的ESD耐压为4000V。

图3-21 4种ESD测试模式

通常ESD水平分为三级:0~1999V为一级;2000~3999V为二级;4000~8000V为三级;对于一些特殊的应用,ESD耐压要求超过10000V,那就是在三级的基础上继续往上增加ESD电压,直到所加电压超过10000V,并且测试引脚的电流-电压曲线没有变化,表明该芯片的ESD耐压可以高达10000V。

(3)ESD的保护

为了避免集成电路被静电打坏,因此在电路中必须设计称为ESD保护结构的相关电路模块,这种保护结构有别于电路中产生正常功能的工作电路模块,因为从该集成电路的功能方面考虑是不需要这部分ESD保护结构的,只是为了避免集成电路中的工作电路模块成为ESD的放电通路而遭到损毁,确保在任意两芯片引脚之间发生的ESD都有适合的低阻旁路将ESD电流引入电源线。这个低阻旁路不但要能吸收ESD电流,还要能钳位工作电路的电压,防止工作电路由于电压过载而受损,而在电路正常工作时,ESD保护结构是不工作的,因此ESD保护电路还需要很好的工作稳定性,能在ESD发生时快速响应。(https://www.xing528.com)

(4)ESD保护电路的设计

随着超大规模集成电路工艺的高速发展,ESD保护能力反而下降,就算把ESD保护器件的尺寸加大,其ESD耐压值也不会被升高,同时由于这种器件尺寸增大导致芯片面积也增大,因此采用适当的ESD保护结构显得非常重要。不同的ESD保护结构所能承受的抗ESD能力各不相同。

ESD保护电路的设计应同时遵循以下3条基本原则:

1)ESD发生时该保护电路要提供从压焊点到地的低阻抗通路,以释放压焊点上积累的静电。

2)ESD发生时,该保护电路要把压焊点的电压钳制在低于被保护电路的击穿电压。

3)在电路正常工作时,该电路具有大的阻抗和很小的电容,保证增加了ESD保护电路而带来的I/O信号延时尽可能小(或者在设计I/O电路时就把ESD保护电路所带来的延时考虑在内),以至于对电路的正常工作不产生明显的影响。

除此之外,ESD保护电路的设计中还应注意以下问题:

1)ESD保护电路自身对ESD有足够高的抵抗能力。

2)在芯片正常工作时,能传输I/O信号,本身处于不被激活的状态。

3)在尽可能小的版图面积中提供尽可能高的ESD保护能力,尽可能利用芯片空余面积,从而不至于使芯片成本上升太多。

4)ESD保护电路设计中要防止上面提到的“闩锁效应”。例如把输出级的PMOS管和NMOS管隔开一定的距离,并加上“保护环”。

5)版图布线的时候,应在ESD通路中注意走线的宽度,并尽量多打通孔。

6)版图布线的时候,应该避免芯片工作电路的走线与ESD保护结构的走线“共线”(即使两者是同一根信号线,最好也分别走线),否则ESD大电流所引起的金属线过热断路会导致工作电路本身发生故障。

7)在CMOS工艺中ESD保护电路的制造应该不增加额外的工艺步骤或者掩膜版数量。

8)ESD保护电路的设计,要能够提升芯片所有引脚的ESD故障临界电压,而不是只提升某几个引脚的ESD防护能力而已。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。