一、时序逻辑电路的分析方法

时序逻辑电路是以触发器为基本单元的逻辑电路,简称时序电路,是数字系统中非常重要的一类逻辑电路。常见的时序逻辑电路有计数器、寄存器、移位寄存器和序列信号发生器等。

与组合逻辑电路相比,时序逻辑电路的特点是任一时刻的输出状态不仅与输入变量有关,还与初始化状态有关。如图4-2-1所示,时序逻辑电路由组合逻辑电路和存储逻辑电路两部分组成,在存储电路中存在反馈回路。

从图4-2-1中可以看出,X为时序逻辑电路的输入信号,Y为输出信号;存储电路D触发器的输入信号D是组合逻辑电路输出的信号,存储电路的输出信号Q、 反馈到组合逻辑电路的输入端,与输入信号X一起决定组合逻辑电路的输出状态Y。

反馈到组合逻辑电路的输入端,与输入信号X一起决定组合逻辑电路的输出状态Y。

图4-2-1 时序逻辑电路图

二、寄存器

在数字电路中,用来存放二进制数据或代码的电路称为寄存器。

寄存器是数字系统常用的逻辑部件,用来存放数码或指令等,它由触发器和门电路组成。一个触发器只能存放一位二进制数,存放n位二进制时,要n个触发器。

寄存器按照功能分,可分为数码寄存器和移位寄存器两种。

(一)数码寄存器

1.电路组成

用来存放二进制数码的寄存器称为数码寄存器。如图4-2-2所示,该数码寄存器由4个边沿D触发器组成4位数码寄存器。

图4-2-2 数码寄存器逻辑电路

2.逻辑功能

图4-2-2中CR为置0端,当CR=0时,4个D触发器的输出都为0,即 Q3Q2Q1Q 0=0000。

边沿触发器D是下降沿触发,当CR=1,CP的上升沿到来时,4个触发器的输入信号才会送入到触发器中,使得 Q3Q2Q1Q 0=D3D2D1D0。

该数码寄存器中D触发器是同时被触发的,输入信号是同时被送入的,输出信号也是同时输出,那么这种方法称为并行输入、并行输出。

(二)移位寄存器

在移位脉冲的作用下,寄存器中的数据可以依次向左或向右移一位,称为左移或右移。这种采用逐位左右移位的寄存器可以分为单向移位寄存器和双向移位寄存器。

1.单向移位寄存器

(1)电路组成。

图4-2-3(a)为单向右移寄存器,图4-2-3(b)为单向左移寄存器,由4个边沿D触发器组成,输入信号是并行输入,脉冲信号是上升沿触发。

(2)逻辑功能。

如图4-2-3(a)所示,以单向右移寄存器为例,低位触发器的输出端Q作为下一级触发器D的输入信号,即 D1=Q0、D2=Q1、D3=Q2。串行口输入端为触发器D0的输入端,输入端如果是4位数,需要经过4个脉冲后,可以从触发器D0~D3的输出端Q输出,实现并行输出。这就是串行输入、并行输出。

图4-2-3 单向移位寄存器逻辑电路

四位右移移位寄存器数据移动表如表4-2-1所示。

表4-2-1 四位右移移位寄存器数据移动表

2.双向移位寄存器

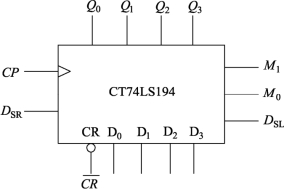

如图4-2-4所示,该寄存器是双向四位移位寄存器,同时具有左移和右移功能。除了具备左移和右移的两个串行输入端外,还应有左移、右移控制端。

74LS194的功能表如表4-2-2所示,功能说明如下:

(1) 是异步清零端。当为0时,输出端置0;当为1时,输出状态与输入相关。

是异步清零端。当为0时,输出端置0;当为1时,输出状态与输入相关。

(2)M0、M1是工作方式控制端。当其值为00时,4个触发器保持原始状态不变;当其值为01时,此时的工作方式为左移移位;当其值为10时,此时为右移移位;当其值为11时,此时为并行输入方式。

图4-2-4 74LS194的引脚排列

表4-2-2 74LS的功能

三、计数器

计数器是用来实现累计电路输入CP脉冲个数功能的时序电路。在计数功能的基础上,计数器还可以实现计时、定时、分频和自动控制等功能,应用十分广泛。

计数器按照CP脉冲的输入方式可分为同步计数器和异步计数器。同步电路中的触发器共用一个时钟,而异步电路由于电路中的触发器不是共用一个时钟,就要特别注意状态的变化与时钟一一对应的关系。

计数器按照计数规律可分为加法计数器、减法计数器和可逆计数器。

计数器按照计数的进制可分为二进制计数器(N=2n)和非二进制计数器(N≠2n),其中,N代表计数器的进制数,n代表计数器中触发器的个数。

(一)二进制计数器

如图4-2-5所示,异步二进制加法计数器由3个JK触发器构成。JK触发器的输入信号J、K都接高电平信号,上一级的JK触发器的输出信号作为下一级JK触发器的时钟脉冲信号,由于同一时刻各触发器Q输出不相同,故3个触发器的动作时间不相同。每个触发器都是下降沿触发,其功能分析如下:

F0:J0=K0=1,每来一个时钟脉冲的下降沿(即C由1变0)时翻转一次。

F1:J1=K1=1,当 Q0的信号从状态1跳变成状态0时翻转。

F2:J2=K2=1,当Q1的信号从状态1跳变成状态0时翻转。

图4-2-5 异步二进制加法计数器

图4-2-5可以体现计数器的计数功能。从图中可以看出,每当一个时钟脉冲下降沿触发过后,计数器输出端就体现脉冲个数。如第一个脉冲下降沿过后,输出端输出Q2Q1Q 0=001;第二个脉冲下降沿过后,输出端输出 Q2Q1Q 0=010;第三个脉冲下降沿过后,输出端输出 Q2Q1Q 0=011…所以这是一个二进制异步加法计数器。

第八个脉冲下降沿过后,输出端输出 Q2Q1Q 0=000,随后随着时钟脉冲下降沿的触发,输出状态从头开始计数。所以该二进制计数器是一个八进制计数器,其状态真值表如表4-2-3所示,其波形如图4-2-6所示。

表4-2-3 3位二进制加法计数器真值表

图4-2-6 异步二进制加法计数器波形图

(二)同步二进制加法计数器

同步计数器是指所有触发器的时钟脉冲信号都来自一个触发脉冲,触发器的翻转和时钟脉冲同步,速度快,工作效率高。同步二进制加法计数器规律和异步二进制加法计数器的规律一样,其状态转换真值表如表4-2-3所示。

如图4-2-7所示,同步二进制加法计数器由3个JK触发器构成,接同一个脉冲信号C,下降沿触发;上一级的输出Q作为下一级J、K输入端的信号。该电路的分析如下:

(https://www.xing528.com)

(https://www.xing528.com)

图4-2-7 由JK触发器组成的3位同步二进制加法计数器

F0:输入信号J0=K0=1,在脉冲信号C下降沿过后翻转。

F1:输入信号J1=K1=Q0,在脉冲信号C下降沿过后翻转。

F2:输入信号J 2=K 2=Q1Q 0,在脉冲信号C下降沿过后翻转。

图4-2-8可以体现计数器的计数功能。该二进制计数器是一个八进制计数器,其分析和异步二进制加法计数器类似。

图4-2-8 同步二进制加法计数器波形图

(三)集成计数器

1.集成同步计数器74LS161

74LS161是一种同步四位二进制加法集成计数器,其管脚排列图如图4-2-9所示,逻辑功能表如表4-2-4所示。

图4-2-9 74LS161管脚排列图

计数器工作原理

表4-2-4 74LS160/161逻辑功能表

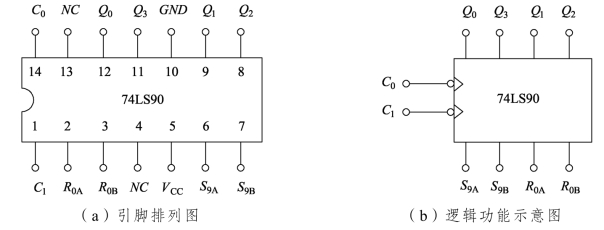

2.集成异步计数器74LS90

74LS90是一种异步二-五-十进制加法集成计数器,它既可以作二进制加法计数器,又可以作五进制和十进制加法计数器。其管脚排列图如图4-2-10所示,逻辑功能表如表4-2-5所示。

图4-2-10 74LS90

R0A、R0B对计数器清零,S9A、S9B将计数器置9。具体功能如下:

(1)计数脉冲信号C0输入时,Q0作为输出端,为二进制计数器。

(2)计数脉冲信号C1输入时,Q3Q2Q1作为输出端,为异步五进制加法计数器。

(3)若将C1与Q0相连时,计数脉冲由C0输入,Q3Q2Q1Q 0作为输出端,构成异步8421码十进制加法计数器。

(4)若将C0与 Q3相连时,计数脉冲由C1输入,Q0Q3Q2Q1作为输出端,则构成异步5421码十进制加法计数器。

(5)清零。

R0A、R0B都为1,S9A、S9B中有时,实现异步清零功能,即 Q3Q 2Q1Q 0=0000。

(6)置9功能。

S9A、S9B都为1,R0A、R0B中有0时,实现置9功能,即 Q3Q2Q1Q 0=1001。

表4-2-5 74LS90逻辑功能表

(四)N进制计数器

1.由触发器构成的计数器

由触发器组成的N进制计数器的一般分析方法是:对于同步计数器,由于计数脉冲同时接到每个触发器的时钟输入端,因而触发器的状态是否翻转只需由其驱动方程判断。由于异步计数器中各触发器的触发脉冲不尽相同,所以触发器的状态是否翻转除了考虑其驱动方程外,还必须考虑其时钟输入端的触发脉冲是否出现。

以JK触发器构成计数器为例,图4-2-11所示是一个同步十六进制计数的电路图,其触发器的状态分析如下:

图4-2-11 同步16进制计数器

F1:J1=K1=1,在脉冲信号C下降沿过后翻转。

F2:J2=K2=Q1,只有当Q1=1时,才在脉冲信号C下降沿过后翻转,否则保持不变。

F3:J 3=K 3=Q1Q 2,只有当Q1=1、Q2=1时,才在脉冲信号C下降沿过后翻转,否则保持不变。

F4:J 4=K 4=Q3Q2,只有当Q3=1、Q2=1时,才在脉冲信号C下降沿过后翻转,否则保持不变。

根据每个触发器的J、K信号即翻转条件,可得到 Q4Q3Q2Q1的状态图,如图4-2-12所示。从状态图上可知,每输入16个脉冲后,计数完成一个工作循环,

图4-2-12 状态图

通过状态图可以确定该电路是按二进制码递增的方向转换的,它能根据电路的状态判断有几个时钟脉冲,所以这个电路称为同步二进制加法计数器,也称为四位二进制加法计数器。其共有16个状态,又称为16进制计数器。

2.由集成芯片构成的计数器

利用集成二进制或十进制计数器可以方便地构成N进制计数器,采用的方法有反馈清零和反馈置数法。以集成芯片74LS161为例。

(1)反馈清零法。

如图4-2-13(a)所示,利用计数器的清零作用,在达到计数过程中的某一个状态时,迫使计数器清零返回重新计数,从而达到N进制计数的功能。

在前面已经介绍74LS161各引脚的功能,如图4-2-13(a)电路所示,清零端CR与时钟脉冲无关,只要CR出现有效信号0,计数器就立刻清零。 端的输入信号来自与非门,与非门的两个输入端信号为 Q3、Q2,要想

端的输入信号来自与非门,与非门的两个输入端信号为 Q3、Q2,要想 端出现有效信号,只需 Q3、Q2同时输出为1时即可。74LS161是一个四位二进制加法计数器,随着脉冲信号的输入,输出 Q3Q2Q1Q 0的状态从0000开始计数,当计数状态到1011时,再来一个计数脉冲使得 Q3Q2Q1Q 0=1100。这个状态是一个短暂的过渡状态,电路会马上清零,使得 Q3Q 2Q1Q 0立刻返回到0000状态开始重新计数周期。由于1100状态只存在很短的一瞬间,不能稳定维持,故该电路的稳定状态是0000~1011,共12个状态,所以该电路为十二进制计数器。

端出现有效信号,只需 Q3、Q2同时输出为1时即可。74LS161是一个四位二进制加法计数器,随着脉冲信号的输入,输出 Q3Q2Q1Q 0的状态从0000开始计数,当计数状态到1011时,再来一个计数脉冲使得 Q3Q2Q1Q 0=1100。这个状态是一个短暂的过渡状态,电路会马上清零,使得 Q3Q 2Q1Q 0立刻返回到0000状态开始重新计数周期。由于1100状态只存在很短的一瞬间,不能稳定维持,故该电路的稳定状态是0000~1011,共12个状态,所以该电路为十二进制计数器。

图4-2-13 74LS161芯片构成的计数器

根据分析,画出该电路的状态图,如图4-2-14所示。

图4-2-14 电路状态图

(2)反馈置数法。

如图4-2-13(b)所示,利用计数器的置数功能,在达到计数过程中的某一个状态时,迫使计数器重新置数开始新的计数,从而达到N进制计数的功能。

前面已经介绍了74LS161各引脚的功能,如图4-2-13(b)所示电路,置数端LD与时钟脉冲无关,只要 出现有效信号0,计数器就置数,使计数器的输出Q3Q2Q1Q 0=D3D2D1D0,重回到计数起点位置。

出现有效信号0,计数器就置数,使计数器的输出Q3Q2Q1Q 0=D3D2D1D0,重回到计数起点位置。 端的置数指令来自与非门,而与非门的3个输入端信号为 Q3、Q1、Q0,要想

端的置数指令来自与非门,而与非门的3个输入端信号为 Q3、Q1、Q0,要想 端出现有效信号,只需 Q3、Q1、Q0同时输出为1时即可。74LS161是一个四位二进制加法计数器,随着脉冲信号的输入,输出Q3Q2Q1Q 0的状态从0000开始计数。当计数状态到1011时,通过与非门使

端出现有效信号,只需 Q3、Q1、Q0同时输出为1时即可。74LS161是一个四位二进制加法计数器,随着脉冲信号的输入,输出Q3Q2Q1Q 0的状态从0000开始计数。当计数状态到1011时,通过与非门使 端为0,为置数做准备。再来一个计数脉冲使得计数器重置,

端为0,为置数做准备。再来一个计数脉冲使得计数器重置, 端有效信号消失,重新从0000状态开始新的技术周期,故该电路的有效状态是0000~1011,共12个状态,所以该电路为十二进制计数器。

端有效信号消失,重新从0000状态开始新的技术周期,故该电路的有效状态是0000~1011,共12个状态,所以该电路为十二进制计数器。

根据分析,画出该电路的状态图,如图4-2-15所示。

图4-2-15 状态转换图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。