采用离子注入技术,可以改变硅的掺杂特性和应力特性。利用光刻掩膜、不同角度、不同注入能量和剂量的并行效果,可以构成在一维和二维尺度范围内的多维度结构和掺杂层,用于调整沟道区的电学特性。其目的多为获得和改善MOSFET器件的电学特性及可靠性性能。常见的电学特性有高掺杂源漏区(n+/p+Source/Drain implant),阈值电压Vt的控制(尤其是兼容不同尺度的沟道长宽CMOS器件的Vt控制,ΔVtimplant、Pocket Implant),沟道漏电流的控制(Anti-Punch through implant),降低热电子效应以提高MOSFET可靠性(LDD implant,lightly doped drain)。此外,采用离子注入技术,可以改变硅的张力特性,形成异质结薄膜淀积结构,用于提高源漏区的结深及其施加一定的张应力提高载流子的迁移率。集成电路常用离子注入如图5-73所示。

1.离子注入层:源漏层欧姆接触

高掺杂源漏层用于制作M-S欧姆接触,为了使接触良好,以减小接触电阻,往往在金属与半导体交界的区域形成高掺杂区,依据掺杂种类被称为n+或者p+。依图5-74所示只有在Si的掺杂达到很高的(>1E19cm-3)时,耗尽层的厚度

图5-73 集成电路常用离子注入

图5-74 集成电路常用离子注入:深度、浓度、用途及其对应的注入元素、注入剂量、注入能量

图5-75 MS(Metal/Semiconductor)欧姆接触能带(只有在高掺杂的情况下才有量子隧穿发生)

(a)热发射(b)欧姆场发射(c)隧穿

Xd≤2.5~5 nm,电子才可以以隧穿的方式穿越于金属与半导体之间,I-V特性才呈线性,即所谓的Ω接触。否则,MS接触为二极管特性的整流接触,接触电阻也偏大且正反向不对称。

接触电阻可以表达为

式中,φB是金属半导体接触势垒之差,N为掺杂浓度,m*为有效质量。可见,掺杂浓度对接触电阻有很重要的影响。图5-75示出了接触电阻和掺杂、不同M-S接触势垒的关系。

图5-76 接触电阻和掺杂、不同MS接触势垒的关系(S.Swirhun,PhD Thesis,Stanford Univ.1987)

2.离子注入层:Vt和沟道漏电流的控制

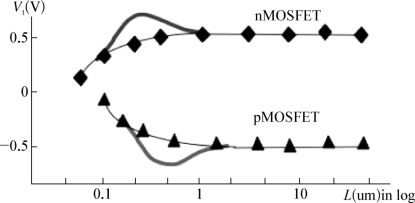

对于MOSFET,沟道区的掺杂浓度、沟道的长度、宽度都会对阈值电压Vt造成影响,造成不同尺度与类型的MOSFET的Vt之间的差异。控制不同尺度和类型的Vt对于实现器件乃至整个电路系统的特性和功能都是至关重要的,尤其是对于整个系统,同一类器件的Vt的涨幅范围必须控制在一定的范围之内(见图5-77)。

图5-77 Vt和沟道漏电流的控制

由图可知,nMOSFET和pMOSFET Vt随沟道长度的减小而减小(绝对值),称为VtRoll-off。通过沟道掺杂和halo的调整(红线和绿线),减少了这个VtRoll-off效应,但是,沟道宽度也会造成Vt的变化,所以也会看到Vt在L减少时有一个小幅度的增加,对于IC整个电路的设计而言,要考虑到所有尺寸MOSFET的电学参数以得出正确的总体电路特性。

对于常规的长沟道MOSFET器件,Vt的控制主要是靠调整沟道区反型层下面的掺杂浓度来产生需要的ΔVt(见图5-78)。对于短沟道器件,由于源漏区耗尽层的对沟道区的侵入,仅靠沟道区的Vt掺杂来调整Vt是不够的,必须靠调整源漏区和沟道区边界处的掺杂(HALO,or Pocket),这种掺杂一般是靠带有角度的离子注入来实现的,角度的可选项多为7°、25°和45°。

图5-78 集成电路常用离子注入及其对应的注入剂量、注入能量、注入角度(https://www.xing528.com)

图5-79 Drain Induced Barrier Lowing(DIBL)

注:由于漏极电压引起耗尽层的扩张引起的沟道势垒的降低。

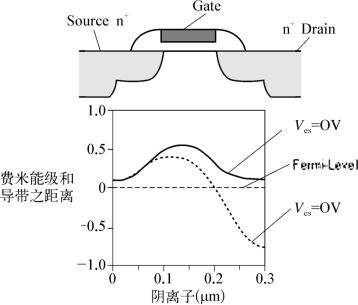

而对于沟道漏电流的控制,主要是针对短沟道效应而导致的源漏耗尽层相接(Punch through),从而引发的p-n结势垒的降低(DIBL)而造成的源漏漏电。从图5-79的能带图上可以看到,由于漏极电压引起耗尽层的扩张,进而引起整个沟道势垒的降低而引起沟道的漏电。

调整沟道区的掺杂可以提升费米能级而得到抑制DIBL的效果,这就是Antipunchthrough implant(见图5-80),它是一个Si沟道体内的埋层形的深度离子注入。通常可以通过计算机模拟的方法估算需要注入的离子剂量和注入能量,以及其后的退火效果对于离子注入分布带来的影响。然后还要通过实验进行进一步的验证得到准确的预期器件电学特性。

图5-80 Anti-punchthrough implant

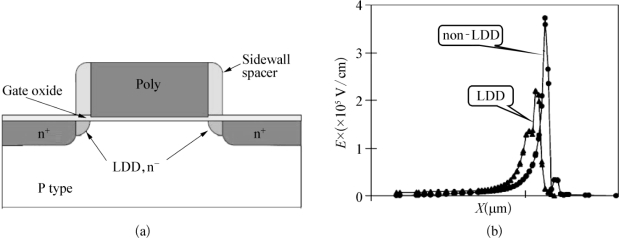

3.离子注入层:LDD离子注入层对于MOSFET可靠性的提高

热载流子是器件可靠性研究的热点之一。特别对于亚微米器件,热载流子失效是器件失效的一个最主要方面。MOSFET通过加入LDD区,使结区电场减弱(见图5-81)来降低热电子效应引起的器件退化。图5-81(a)的计算机模拟结果说明LDD缓冲层降低了漏极的电场强度,从而有力地降低了热载流子的温度(能量),有效地减低了热载流子对栅氧化层的注入和破坏作用,提高了器件的可靠性。在实用工艺中,LDD会增加源漏极的串联电阻,所以要综合考虑LDD掺杂的浓度与深度、宽度,通常会采用计算机模拟的方法来优化LDD的各项参数指标,然后以实验验证之。

图5-81 LDD离子注入结构

(a)F.Duan etc进行的计算机仿真模拟结果(b)同一沟道电压下的MOSFET源漏端的电场分布

注:图(b)中三角形的点为引入LDD后的电场分布,可以看到,LDD使电场分布变得平缓,强度也有所降低。

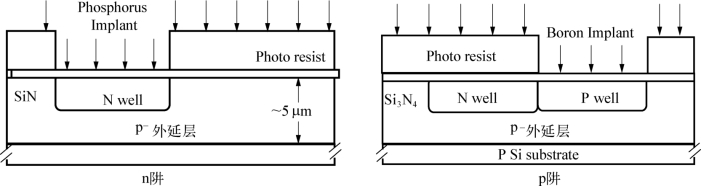

4.双阱CMOS工艺:高能量离子注入层产生n阱层和p阱层

CMOS电路中既包含NMOS晶体管也包含PMOS晶体管,NMOS晶体管是做在P型硅衬底上的,而PMOS晶体管是做在N型硅衬底上的,要将两种晶体管做在同一个硅衬底上,就需要在硅衬底上制作一块反型区域层,该区域被称为“阱”。而“阱”层的形成多为在低掺杂的硅衬底上用高能量离子注入加高温退火推进结深的方法而形成。

根据器件的性能需要和优化条件,阱层的掺杂浓度和密度分布可以通过注入能量、剂量和退火条件(时间和温度)进行调动。CMOS工艺分为p阱CMOS工艺、n阱CMOS工艺以及双阱CMOS工艺(见图5-82)。其中n阱CMOS工艺由于工艺简单、电路性能较p阱CMOS工艺更优,从而获得广泛的应用。近年来由于RF器件在市场上的需要,双阱CMOS工艺得到了长足的应用,用来隔离硅衬底而降低硅衬底的高频损耗。在未来,引入的SOI可以规避CMOS所要求阱层工艺,优点是节省了一系列的隔离面积和杜绝了CMOS中n阱和p阱所带来的栓锁效应(Latch up)。

5.引入应力层提高半导体器件的迁移率

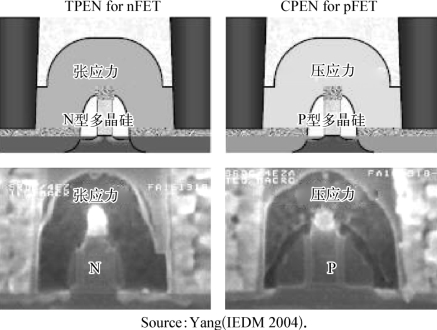

衬底诱生应力、工艺诱生应力和采用不同的衬底晶向等三类方法都可以显著提高载流子的迁移率。一般来讲,张应力可以提高电子的迁移率而压应力可以提高空穴的迁移率。对于栅极周围的氮氧化硅薄膜工艺进行控制,可形成张应力和压应力两种类型的氮化硅薄膜。AMD采用该方法制备的双应力层用以提高NMOS和PMOS的电迁移率,从而改善了器件性能(见图5-83)。

图5-82 CMOS工艺:高能量离子注入层产生n阱层和p阱层

图5-83 利用SION薄膜层在NMOS引入张应力TPEN(Tensile Plasma Enhanced Nitride)和pMOS中压应力CPEN(Compressive Plasma Enhance Nitride)

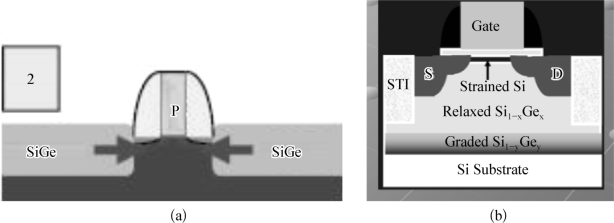

图5-84 采用Si与Ge之间的晶格失配引入应力提高载流子迁移率

(a)利用Si与Ge的晶格失配在nMOS(b)pMOS中引入张应力和压应力来提高电子和空穴的载流子迁移率

在65/45 nm技术工艺中,采用Si和Ge之间的晶格失配(Si的晶格常数是5.4309Å而Ge为5.6575Å)引入应力来提高载流子的迁移率。Intel采用对pMOS源漏极刻蚀后外延锗硅层,从而引入沟道压应力以提高空穴的迁移率(达35%)。IBM在硅锗上引入应变硅(strain silicon)外延,由于硅跟锗硅晶格常数失配而导致硅单晶层受到下面锗硅层的拉伸应力(tensile stress),从而提高了电子的迁移率,提升了nMOS的工作电流。综合这两项,也在一定的程度上提升了CMOS电路的工作电流和性能(几十%),如图5-84所示。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。