大多数数字集成电路(IC)制造厂商都至少会生产一种称之为胶合逻辑[1]①的低发射系列产品。制造厂商也往往会生产几种不同型号的,对静电放电(ESD)具有较好抗扰能力的输入/输出(I/O)IC。有些厂商还为他们的客户提供一些“具有较好EMC性能的”(有些这类的“EMC”微处理器的发射要比普通型号的低出40dB)超大规模IC(VLSI)。

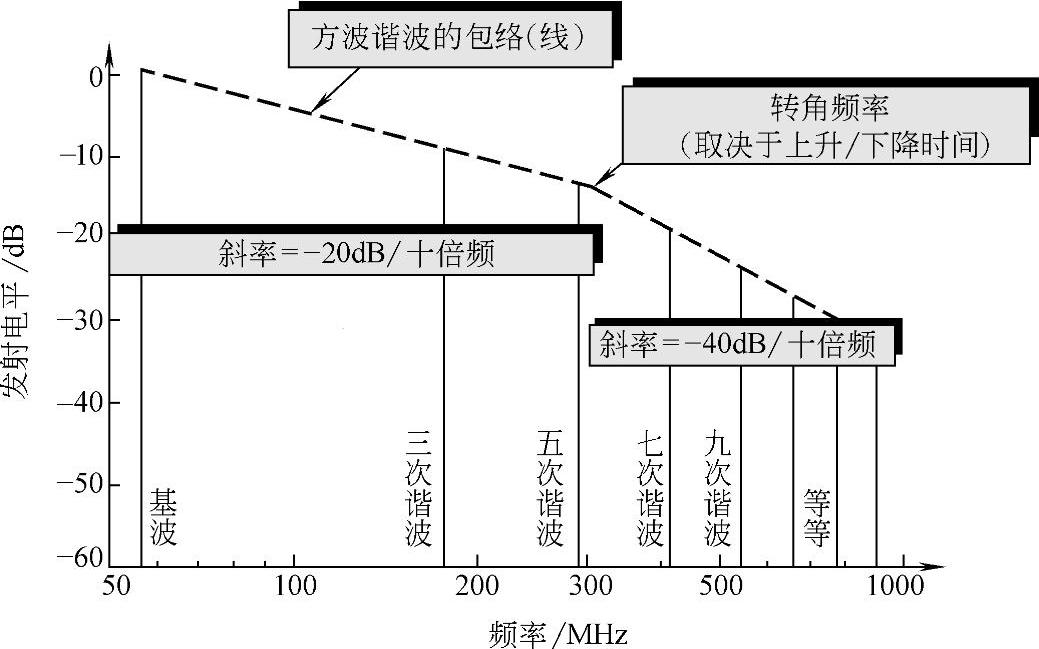

我们知道,大多数数字电路都是以方波作为时钟的。但正如图1-1-1所示,它们恰恰都含有非常丰富的谐波成分。

图1-1-1 一个具有1ns上升和下降时间的理想方波的频谱

如图1-1-1所示,时钟频率越高、其边沿越陡峭,它的谐波频率和发射电平也就越高。

因此,在满足产品技术指标要求的前提下,要选用最低的时钟频率,并尽可能地采用上升沿和下降沿比较平缓的时钟器件。如果高速CMOS[2]②(HC)可用的话,绝不选用先进CMOS[3]③(AC)。同样,当CMOS 400可用的话,绝不选用HC。

要选用具有高度信号完整性和电磁兼容(EMC)较好的IC。下列是一些选择准则和这类元器件的一些实例。

1)选用电源和地参考插针安排得相邻近、并具有多个电源和地参考插针,以及把它们中心化的IC封装。

这些措施都有助于形成电源和地电流通路之间的互感最大化,而又最小化了它们的自感。从而减小了电源电流形成的电流环路区域,以使去耦合变得更为有效。所有这些安排都将会减少EMC的问题和地(电位)起伏。

2)降低输出电压波动以及控制转换速率。

降低输出电压波动以及控制转换速率都可以降低信号的dV/dt和dI/dt,从而可以将发射降低几个分贝。虽然这些技术改善了发射,但在某些情况下,它们有可能会使抗扰性能变坏。所以在使用它们时,很可能需要采取某种折中方案,使两者都有所兼顾。

3)传输线的I/O匹配。

当高速信号必须沿着导体传送时,IC需要具有与传输线相匹配的输出能力。举例来讲,可用的总线驱动器可以驱动一个25Ω的并联终端负载的话,那么它将可以驱动一个25Ω的传输线(例如,随机存取记忆板:RAMBUS),或者驱动2个50Ω的传输线,或者4个100Ω的传输线,或者6个150Ω的传输线(当采用星形联结时)。

4)平衡信号。

平衡信号传输使用±(差分)信号,而不使用0V作为它的信号返回通路。这类IC在驱动高速信号(例如,时钟频率>66MHz)时是非常有用的。这是因为它们可以帮助保持信号的完整性,同时也可以在某种程度上改善共模发射和抗扰性。

5)低地电位波动。

通常来讲,具有低地电位波动的IC的EMC性能也较好。

6)低发射电平。

正如前面已经指出的:大多数数字IC制造厂商都提供有低发射的胶合逻辑系列。例如,ACQ[4]①和ACTQ[5]②系列与AC和ACT[6]③系列相比,前者具有较低的发射。有些厂商还提供EMC性能较好的VLSI系列。例如,Philip公司至少生产有两种EMC类型的80C51微处理器(CPU),它们要比其他类型的80C51产品降噪40dB。(https://www.xing528.com)

7)推荐使用非饱和逻辑。

这是因为它们的上升沿和下降沿时间倾向于较为平滑(受控转换速率)。因此,与像TTL这类饱和逻辑相比,它们的高次谐波电平也就相对较低。

8)选用对静电放电(ESD)和其他骚扰现象具有高等级的抗扰性能的元器件。

选用具有抑制ESD和对其他出现在它们插针上的瞬态具有高等级抗扰水平的串联通信器件(比如,RS232[7]④、RS485[7]⑤)。假如器件未能达到对它们所规定的抗扰性能指标或仅相当于产品所需要的标准和产品所要求的电平时,那就将需要附加抑制元器件。

9)低输入电容。

当逻辑状态发生改变时,低输入电容有助于降低所产生的峰值电流,从而也就降低了磁场发射和地回路电流(两者都是数字发射的主要原因)。

10)低电源瞬态电流。

图腾柱(Totem-Pole)输出级中,当两个输出器件从一个状态转换到另一个状态时,存在一个短暂的周期,在该周期中,两个输出器件都会处于导通状态。因此在这个短暂的周期中,电源电压限值会被短路至0V,并且电源的电流瞬态值可以超过信号的输出电流。该瞬态电流(有时称之为“贯通”电流)和由它在电源限值上引起的噪声是造成发射的主要原因。相关的参数可以包括瞬态电流的峰值,它的dI/dt(或频谱)及总电荷量。所以上列中的任何一个或全部对正确设计电源的去耦电路都是非常重要的。因此只要可能,在设计中就要尽量选用规定有低电流瞬态值的IC。

11)选用的IC输出驱动能力不应大于应用需要值。

一个IC的输出驱动电流(特别是如一个总线驱动器的驱动电流)将不再像过去那样非要超过所需要的值。具有较大额定电流的驱动器具有较大的输出晶体管。这意味着在相当程度上,它能够承受较大的电源瞬态。但是,它们驱动能力的增加意味着它们所驱动的(印刷)线条也可能会经历快于它们所需要的上升和下降时间,从而导致过冲和振铃问题的增加。最终破坏了信号的完整性和较高电平的射频(RF)发射的出现。

所有以上所列的项目都应该在它们的数据手册的技术规范中列出所保证的最低或最高(合理的)值(或者至少是典型值)。

不同来源的元器件(即具有相同型号和技术指标,但来自不同制造厂商的元器件),它们的EMC性能可以具有巨大的差异。所以有时在产品生产过程中,要控制元器件的来源,以确保继续符合EMC性能的要求是十分重要的。我们不推荐在未经EMC性能测试的情况下,就使用不同来源的元器件于产品中。所以,最好的办法就是继续使用当初选定的单一来源的元器件。

高技术的IC供应厂商往往会为他们的产品提供详细的EMC设计指南。如Intel公司就为它的奔腾(Pentium)MMO[8]①IC提供这样的设计指南。所以,在对产品进行初始设计以前,就应该向供应厂商索取这类文件,并严格地按照它们的规定去做。能够向客户提供详细EMC设计指南,说明制造厂商在他们的产品规范中已将客户的实际需要考虑其中。所以当选择元器件时,这一点也许可以作为整体考虑的一部分。

现在有些现场可编程门阵列(FPGA)器件(也许还有其他一些IC)都具有对它们的转换速率、输出驱动能力和/或驱动信号的输出阻抗编程的能力。它们的驱动特征可以被调节到以提供较好的信号完整性以及/或者EMC性能。这样一来,在设计过程中,就可以大大减少更换IC、改变印制电路板(PCB)上的元件值或修改PCB布局。从而也就帮助我们缩短了研发时间。

在IC的EMC性能无从得知的情况下,早期设计阶段的最好选择是对各个不同的竞争对手所提供的元器件进行EMC性能测试。该类测试可以在一个简单的标准功能电路上完成。测试中,至少要包括时钟的运行以及在高速数据运行下的性能。

发射测试可以很容易地在一个标准测试工作台上,在几分钟的时间内完成。该工作台应带有连接到一个频谱分析仪(或一个宽带示波器)的近场磁环探头。测试结果将会清楚地告诉我们,哪些供应厂商的哪些元器件要明显地比其他一些降噪性能好得多。抗扰测试可以使用连接到一个信号发生器(连续的RF或瞬态的)的与上述测试所使用的相同探头。但假如它是一个专用探头(而并不只是一匝短路的导线的话),那么先要检查一下它的功率承受能力是否符合我们的测试要求。

在测试过程中,需要把该近场探头放在几乎与被测元器件或PCB相接触的位置。为了找出它的“最热点”(最敏感点)以及最大化探头取向,首先应该在整个区域中,以沿水平和垂直阵列方式进行扫描(在每个方向上,以相互间为90°的不同取向手握探头)。最后,将注意力集中在信号最强的区域上。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。