1)智能道闸控制系统的硬件组成

智能道闸控制系统的硬件设计主要包括ARM嵌入式基本系统、无线通信激励模块、无线通信模块、RS232串口模块、时钟模块和TCP/IP通信模块的设计等。为了实现以上各模块的功能以及高性能、低价格等要求,本应用在ARM嵌入式基本系统的基础上架构硬件平台,对各个模块的硬件电路进行设计。利用LM3S6965内置通用异步收发器(UART)模块外加RS232收发电路,实现RS232串行通信;利用LM3S6965内置以太网控制器模块外加自带隔离变压器的RJ45网络接口构成网络通信电路。125kHz激励源部分采用PIC16F690单片机、高速MOSFET驱动器及125kHz天线等。无线通信标签以CC2530为主芯片,CC2530具有RF内核控制模拟无线电模块和休眠功能,结合外围的唤醒电路,可完成低功耗、较长距离无线通信的要求。整个系统组成如图8-2所示。

图8-2 智能道闸控制系统组成

2)微处理器LM3S6965简介

在设计主控制器时,根据控制的复杂程度和可靠性等指标要求选择一种性价比合理的嵌入式芯片。本系统选用了基于ARM Cortex-M3内核的LM3S6965作为主控制器的主芯片。

ARM Cortex-M3处理器是从ARM7TM处理器系列移植过来的,为高性能、低成本、低功耗的平台提供一个满足小存储要求的解决方案,它还具有出色的计算性能和优越的中断响应能力。

LM3S6965内部包含了本应用需求的常用接口。其主要特点如下:

(1)32位ARM® CortexTM-M3v7M架构。

(2)50MHz工作频率。

(3)含有256KB Flash和64KB SRAM内部存储器。

(4)10/100Mbps以太网控制器,由完全集成的媒体访问控制(MAC)和网络物理(PHY)接口器件组成。

(5)4个通用定时器模块,每个提供2个16位定时器。

(6)看门狗定时器。

(7)通用DMA控制器。

(8)2个内部集成电路(I2C)模块、1个同步串行端口(SPI/SSP)模块以及3个通用异步收发(UART)模块。

(9)1个正交编码接口(QEI)、模数转化器、模拟比较器以及脉宽调试器(PWM)。

3)主控制器的硬件设计

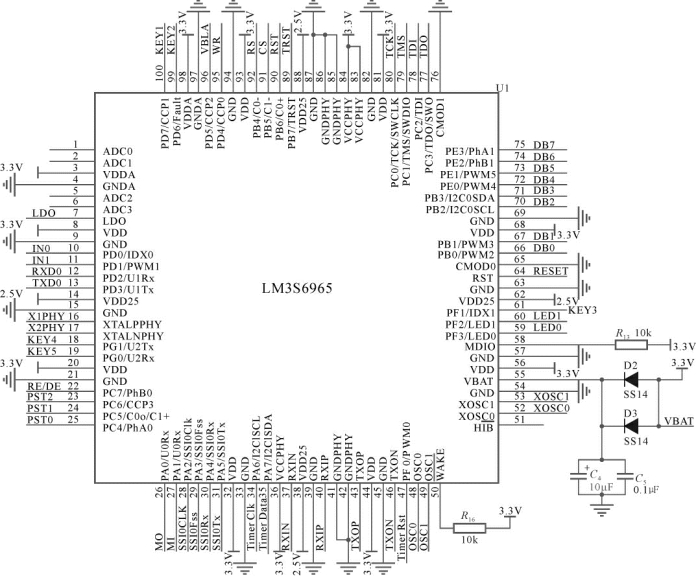

(1)LM3S6965基本系统设计

LM3S6965有4个时钟源可供使用,它们分别为主振荡器、内部振荡器、内部30KHz振荡器和外部实时振荡器。内部振荡器的频率是12MHz±30%,是在上电复位过程中和上电复位之后使用的时钟源,软件以后可切换为另一种可用的时钟源。主振荡器在1 MHz~8.192 MHz的频率下工作,本系统使用外部6 MHz的晶振,微处理器的工作频率可通过内部PLL单元提高。内部30KHz振荡器与内部振荡器类似,它提供30KHz±30%的工作频率,主要用在深度睡眠的节电模式中。外部实时振荡器提供一个低频率、精确的时钟基准,是休眠模块的一部分。

LM3S6965有5个复位源:RESET管脚复位、看门狗复位、上电复位(POR)、内部掉电复位(BOR)和软件启动复位。任何复位源可使芯片复位有效,一旦操作电压到达一个可使用的级别,则启动唤醒定时器。复位将保持有效直至外部的复位被撤除,振荡器开始运行。当计数经过了固定的时钟个数后,Flash控制器已完成其初始化。

本应用系统采用了上电复位和手动复位相结合的方案,LM3S6965最小系统组成电路如图8-3所示。图8-3中给出了LM3S6965内部各类外设接口与具体功能电路间的引脚连接,包括SPI通信、调试接口、UART通信、以太网通信、LCD接口、SD卡、按键等。

(2)人机交互模块设计

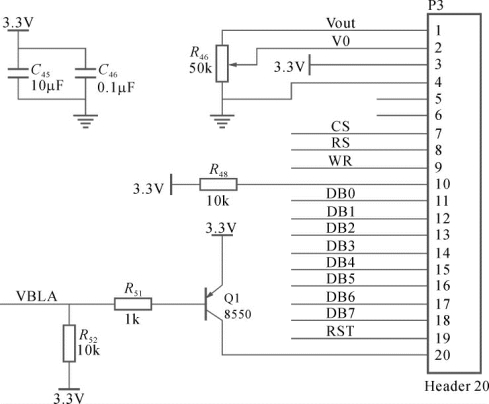

主控制器的显示采用LM1095R液晶显示模块,该显示模块与LM3S6965的硬件连接如图8-3、图8-4所示。

图8-3 LM3S6965最小系统组成电路

图8-4 液晶显示模块与LM3S6965的接口电路

LM1095R是一款192×128点阵中文/图形液晶显示模块,内置RA8803控制器。该模块不仅可以显示单一的文本,还可显示图形,在文本模式下能够实现大小字体的混编(最大字体为64×64),在连续输入信息时,可以自动设定行距,使显示画面更加美观,大大节省用户的开发时间。其主要特点有:

①单电源供电,内置升压电路;

②高对比度,FSTN型LCD屏;

③白色LED背光;

④内嵌简体中文字库(7 602个汉字);

⑤双图层内存(2×9.6K显示存储器);

⑥可自定义16个字符。

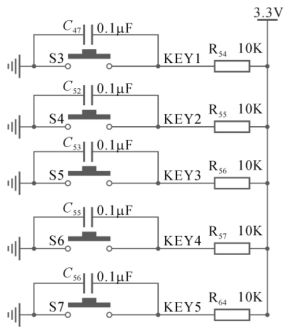

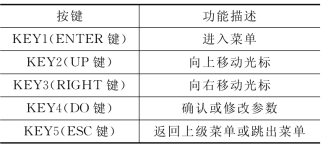

按键模块采用了5个按键来实现按键输入功能。键盘控制是根据按键按下时引起的电平高低变化来判断具体哪个按键按下,然后执行相对应的操作,5个按键的设计如图8-5所示。按键功能如表8-1所示。

图8-5 按键电路

表8-1 按键功能

(3)网络模块设计

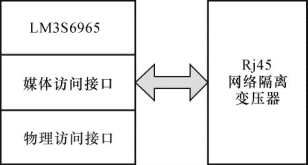

LM3S6965内置以太网控制器。以太网控制器由一个完全集成的媒体访问控制(MAC)和网络物理(PHY)接口器件组成,完全支持10BASET和100BASE-TX标准,只需要一个双路1∶1隔离变压器就能与网络相连。网络通信模块如图8-6所示。

图8-6 网络通信模块

以太网控制器中的物理层(PHY)包括集成的编码解码器、扰码器、解扰器、双速时钟恢复和全功能自协商功能。发送器包含一个片内脉冲整形器和一个线路驱动器。接收器有一个自适应均衡器和一个校准时钟及恢复数据所需的基线恢复电路。PHY层有一个片内晶体振荡器,这个振荡器也可由一个外部振荡器驱动。

(4)数据存储模块硬件设计

SD卡(Secure Digital Memory Card)是一种基于半导体快闪记忆器的新一代记忆设备,重量只有2克,但却拥有高记忆容量、快速数据传输率、极大的移动灵活性以及很好的安全性,目前在嵌入式系统中已取得越来越广泛的应用。

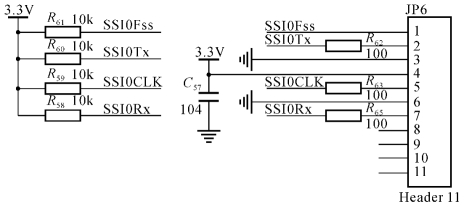

对SD卡进行软硬件设计首先要选择SD卡的总线模式。SD卡有两种总线模式:SD总线模式和SPI总线模式。本系统采用SPI模式。

SD卡共有9个引脚。在SPI模式下,SD卡1—7号引脚依次为片选引脚SSEL、数据输入MOSI、电源地、电源VDD、时钟信号SCK、电源地、数据输出MISO,8脚与9脚在SPI模式下保留未用。由于SPI总线通信协议要求在空闲时SPI总线应保持高电平,因此SSEL、MISO、MOSI、SCK引脚应外接10K上拉电阻。

SD卡与LM3S6965的硬件接口如图8-7所示。

图8-7 SD卡与LM3S6965的硬件接口

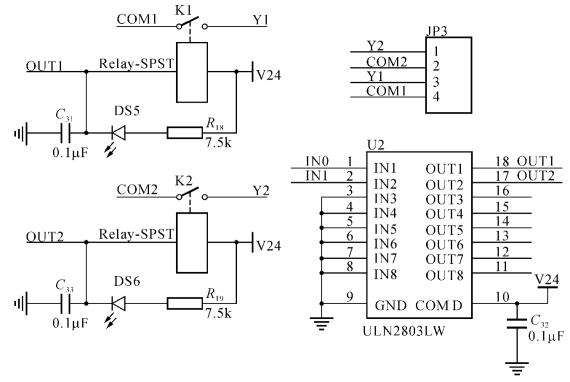

(5)道闸控制开关电路设计

主控制器控制道闸开关的电路如图8-8所示,其中Y1为开启道闸的输出端,Y2为关闭输出端,COM1和COM2为道闸的公共信号管脚。ULN2803是一款反向输出型芯片。当系统上电稳定后,ULN2803芯片的两个输入管脚为低电平,则对应的输出管脚为高电平,继电器不闭合。当ULN2803芯片的两个管脚IN0、IN1为高电平时,继电器闭合,Y1、Y2分别与其对应的公共端连接,可控制道闸开关。

图8-8 道闸控制开关电路

4)无线通信的硬件设计

无线通信模块主要包括无线通信激励源、无线通信发送标签和无线通信接收标签。无线通信激励源的作用是通过天线不断向外发送125kHz频率的载波信号,使放置在车辆上的无线通信发送标签从睡眠状态激活为正常工作状态。(https://www.xing528.com)

(1)无线通信激励源硬件设计

采用PIC16F690单片机作为无线通信激励源的主芯片。PIC16F690有两个定时器提供必要的上电延时,一个是起振定时器(OST),旨在确保芯片在晶振达到稳定之前始终处于复位状态;另一个是上电延时定时器(PWRT),仅在上电时提供64ms(标称值)的固定延时,用来确保器件在供电电压稳定之前处于复位状态。此外,还有当器件发生欠压时使器件复位的电路,该电路可使用上电延时定时器,提供至少64ms的复位延时。有了这些功能,绝大多数应用就无需再外接复位电路了。

PIC16F690具有的技术特点如下:

①高性能的CPU,仅需学习35条指令;

②精准的内部振荡器;

③节能休眠模式、宽电压工作范围(2.0~5.5V)、工业级和扩展级温度范围;

④增强型USART模块——支持RS-485、RS-232和LIN2.0,I2C;

⑤17个I/O引脚和1个只用作输入的引脚;

⑥2个模拟比较模块,A/D转换器;

⑦3个时钟定时器;

⑧增强型PWM模块。

125kHz载波信号发生电路的设计如图8-9所示。为了增加无线唤醒覆盖范围,图8-9设计了3路无线信号发生电路,分别负责3个方向,确保车上的无线通信标签能被唤醒。

图8-9 125kHz载波信号发生电路

PIC16F690产生125kHz的载波信号(PWN-IN),即唤醒信号,SN74AC08是与门芯片,CS-OUTPUT-A是开关信号。当PIC16F690向外发送125KHz的载波信号时,CSOUTPUT-A信号置高;当该次唤醒信号发送完毕,CS-OUTPUT-A信号置低;当下次发送唤醒信号时,CS-OUTPUT-A信号再次置高。唤醒信号通过功率放大芯片TC4422将信号放大。

(2)无线通信模块硬件设计

无线通信模块分为两部分,一部分称为无线通信发送标签,另一部分称为无线通信接收标签。根据设计需要,需选择一款满足功耗低、可靠性高、稳定性好等要求,又带有无线通信功能的芯片作为无线通信模块的微控制器。所以本系统选用TI公司的CC2530微控制器作为无线通信标签的主芯片。

CC2530使用的8051CPU内核是一个单周期的8051兼容内核。它有3个不同的存储器访问总线(SFR、DATA和CODE/XDATA),以单周期访问SFR、DATA和主SRAM。它还包括一个调试接口和一个18路输入的扩展中断单元。

CC2530包含3个物理存储器:一个8-KB SRAM、一个256 KB闪存存储器和一个XREG/SFR寄存器。8-KB SRAM映射到DATA存储空间和XDATA存储空间的一部分。8-KB SRAM是一个超低功耗的SRAM,当数字部分掉电时(供电模式2和3)能够保留自己的内容,这对于低功耗应用是一个很重要的功能。256KB闪存存储器为应用提供了可编程的非易失性程序存储器,映射到CODE和XDATA存储空间。除了保存程序代码和常量,非易失性程序存储器允许应用程序保存必须保留的数据,这样在设备重新启动之后可以使用这些数据。使用了这个功能,例如可以利用已经保存的网络具体数据,就不需要经过完整的启动、网络寻找和加入过程。

CC2530具有的技术特点如下:

①5种不同的运行模式:主动模式、空闲模式和供电模式1、2、3;

②5个定时器,其中包括一个睡眠定时器。睡眠定时器可将系统从供电模式1、2切换到主动模式;

③5个DMA,可以用来减轻8051CPU内核传送数据操作的负担,从而实现在高效利用电源的条件下的高性能;

④2个UART,它们能够分别运行于异步UART模式或者同步SPI模式;

⑤带有PHY的USB2.0全速控制器的接口;

⑥一个IEEE 802.15.4兼容无线收发器;

⑦看门狗定时器;

⑧极高的接收灵敏度和抗干扰性能;

⑨输出功率高达4.5dBm;

⑩极低的功耗。主动模式RX下24mA,主动模式TX下29mA,供电模式3(睡眠模式)下0.4μA。

CC2530的工作模式分为主动模式、空闲模式、供电模式1、供电模式2和供电模式3。

①主动模式:完全功能模式。稳压器的数字内核开启,16 MHz RC振荡器或32 MHz晶体振荡器运行,或者两者都运行。32kHz RCOSC振荡器或32kHz XOSC运行。

②空闲模式:除了CPU内核停止运行(即空闲),其他部分和主动模式一样。

③供电模式1:稳压器的数字部分开启。32MHz XOSC和16MHz RCOSC都不运行,32kHz RCOSC或32kHz XOSC运行。复位、外部中断或睡眠定时器过期时系统将转到主动模式。

④供电模式2:稳压器的数字内核关闭。32MHz XOSC和16MHz RCOSC都不运行,32kHz RCOSC或32kHz XOSC运行。复位、外部中断或睡眠定时器过期时系统将转到主动模式。

⑤供电模式3:稳压器的数字内核关闭。所有的振荡器都不运行。复位或外部中断时系统将转到主动模式。

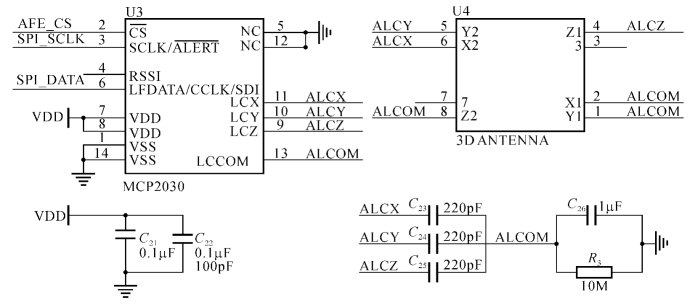

无线通信发送标签放置在汽车内部,平时一直处于供电模式3(即睡眠模式)状态。MCP2030收到无线通信激励源发出的125kHz的特定唤醒信号,给CC2530发送一个脉冲信号作为中断请求,CC2530收到这个外部I/O中断事件,使其从睡眠模式切换到主动模式。

MCP2030是一款独立模拟前端(Analog Front-End,AFE)器件,可用于低频传感和双向通信应用,其电路如图8-10所示。该芯片具有8个可由外部器件读取的可读写内部配置寄存器,还有一个只读的STATUS寄存器。其主要特点如下:

①3个用于输入低频模拟信号的通道,各输入通道可单独使能或禁止;

②高输入检测灵敏度(3mVPP,典型值),最低检测输入信号幅值可低至大约1mVPP;

③高调制深度灵敏度(低至8%);

④3种输出选择(解调数据、载波时钟、接收信号强度指示(RSSI));

⑤输入载波频率为125kHz,最大输入数据速率为10kbps;

⑥双向收发通信;

⑦4μA的低待机电流(使能3个通道时),13μA的低工作电流(使能3个通道时);

⑧与外部器件连接的串行外设接口(SPI);

⑨可编程天线调谐电容。

MCP2030内部没有CPU,所以需要由CC2530通过SPI通信对其内部的寄存器进行配置。

MCP2030的3路输入管脚LCX、LCY、LCZ分别与3D天线的3个管脚相连。所谓3D天线,是在一个铁芯的X、Y、Z轴分别绕线圈,使天线无论处在什么方向,都能很好地接收信号。C23、C24、C25这3个电容是它们各自所在路的输入信号的调谐电容。若要使该路信号的接收质量最好,则电容值与电感值应满足公式![]() ,这里f值为125kHz,而L则是该路上所绕线圈的电感值。

,这里f值为125kHz,而L则是该路上所绕线圈的电感值。

MCP2030的SPI通信的3个管脚CS、SCLK、SDIO直接与CC2530的3个管脚相连。CC2530通过SPI总线配置MCP2030内部寄存器。

图8-10 MCP2030电路

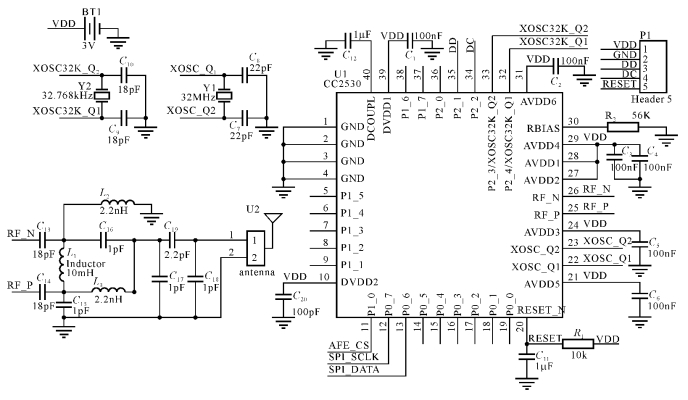

CC2530的电路见图8-11。无线数据通过天线回路接收,经过RF匹配网络,最后传输到芯片RF控制模块中。RF匹配网络是为了保证传输最大的信号能量,减少回波对信号质量和可用功率的影响,保证信号的高质量。U2是2.4GHz天线,C13、C14、C15、C16、C17、C18、L1、L2、L3组成了RF匹配网络。引脚P1.0、P0.7、P0.6用来对MCP2030进行寄存器配置和通信。Y1是32 MHz晶振。CC2530可以选择高精度的晶体振荡器,也可以选择低功耗的高频RC振荡器,但当运行RF收发器时,必须使用32M晶体振荡器。Y2是32.768 KHz的晶振,用来驱动睡眠定时器,为看门狗定时器产生标记。

图8-11 CC2530电路

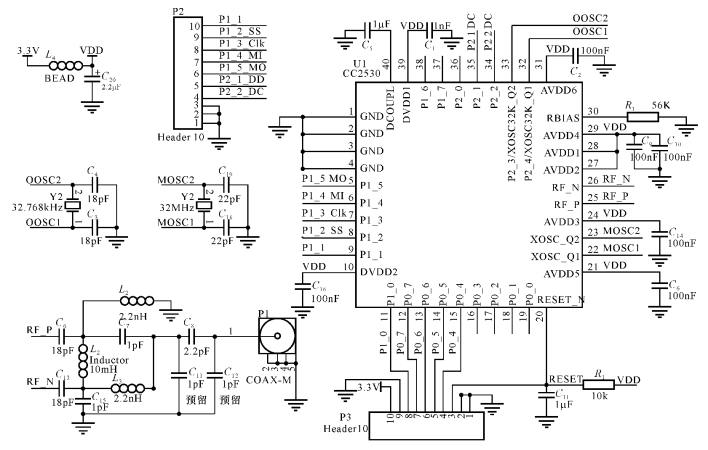

无线通信接收标签电路设计见图8-12,它安装在道闸控制系统的主控板上,由主控板上的3.3V电源直接供电,因此不用进入睡眠模式。无线通信接收标签同发送标签一样,具有同样的RF匹配网络,以保证传输信号的高质量。管脚P1.4、P1.5是CC2530的异步串行通信收发接口。当无线通信接收模块收到发送模块发送的数据后,异步串行通信接口即向主控板上的MCU发送数据。

图8-12 无线通信接收标签电路

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。