1.概述

随着器件集成度的增加,晶片表面无法提供足够的面积来制作所需的互连线,为了配合MOSFET晶体管缩小后所增加的互连线需求,为了缩短器件间或器件与周边的通信时间,必须采用两层以上的3D金属化连线设计。基本上,多重金属互连线的制作是在完成器件的主体后才开始的,所以这个制作过程可以视为独立的半导体工艺流程,称为后段制作工序(BEOL,Back End of Line)。

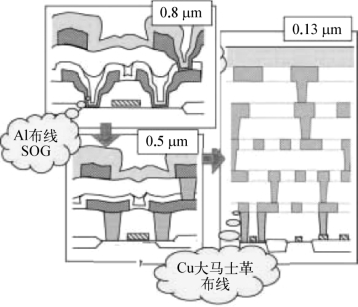

20世纪90年代末,金属连线体系由传统的Al连线系列过渡到Cu连线的系列(见图5-88),工艺程序也有了很大的不同。最早的0.8μm工艺只用一层Al淀积来实现互联,然后由于小尺寸孔径的台阶覆盖问题采用栓塞(VIA)来连接上下的两层铝金属,到了0.13μm工艺以后,后端工艺采用Cu代替了Al,采用的是镶嵌工艺(damascene)也称为大马士革工艺方法,将铜互连工艺栓塞和铜连线工艺整合成一体化。铜图形化方法镶嵌工艺(damascene)最早在1997年9月由IBM提出来的,它采用对介电材料的腐蚀来代替对金属的腐蚀来确定连线的线宽和间距。镶嵌工艺分为单镶嵌和双镶嵌(Dual damascene)。它们的区别就是在于穿通孔和本身的工艺连线是否是同时制备的。除此之外,阻挡层、Cu淀积籽晶种子层、化学机械抛光技术(CMP)是铜互联工艺的几项相关关键技术。

图5-88 金属连线层发展历史,栓塞(VIA)的引入,由Al到Cu的变迁

表5-8示出了设计规则从0.8μm到0.13μm的变化过程中,布线层数、新材料和新工艺方法的引入和发展。

表5-8 设计规则从0.8μm到26 nm的变化过程中,布线层数、新材料和新工艺方法的引入和发展

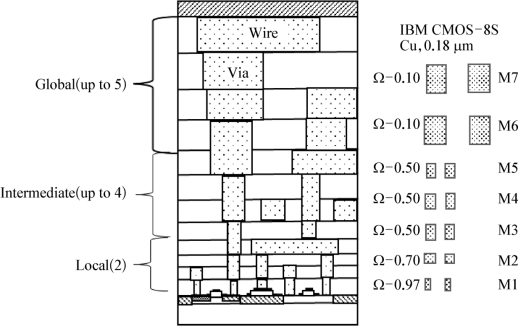

而作为后端工艺,Cu互联连线系统成为IC设计制造的一个系统化工程。时至2014年,集成电路芯片上可以集成上亿个有源器件,而每个器件都须具备与外界通信的导体连线,必须采用3D连线结构,金属导电的层数已达到十几层以上,金属连线也按照元器件和电路、模块的功能分层次布局。通常,金属层结构划分为三大类(见图5-89)。

图5-89 多重金属互连线的三类体系

图5-90 SEM:多重金属互连线的三类体系

注:可以明显的看出连线的三个层次,上面的金属层尺度上压大很多

最底层的第一、第二层多用于本地的短线连接,比如SRAM存储单元的内部连接、各种CMOS反相器、与非门、逻辑门的单元设计,等等。

中间的四五层多用于单元之间的中距离互联,这一层的金属比第一层要宽、要厚,以保证足够的导电性能。

最上面的几层更宽更厚,用于模块之间的长距离连接。

图5-90展示了SEM实际的这三个层次的金属连线结构。

而就多层复合金属化体系材质而言,后端工艺体系需由多种不同功能的导电薄膜与绝缘薄膜层组成:导电层包括半导体接触层(salicide),过渡层(缓冲层,如TiN、W)和金属连线层(如铝、铜)。

2.半导体接触层

金属与半导体是两种不同类的材料,它们之间构成MS结,之间会有势垒差异,须在两者之间建立良好的欧姆接触。适用集成电路的主要材料是金属硅化物(salicides),金属硅化物在VLSI/ULSI器件技术中起着非常重要的作用,被广泛应用于源漏极和硅栅极与金属之间的接触,自对准硅化物(selfaligned silicide)工艺已经成为超高速CMOS逻辑大规模集成电路的关键制造工艺之一。该工艺减小了源/漏电极和栅电极的薄膜电阻,降低了接触电阻,并缩短了与栅相关的RC延迟。另外,它采用自对准工艺,无须增加光刻和刻蚀步骤。在深亚微米技术中形成的金属硅化物薄膜主要有硅化钛、硅化钨、硅化钴、硅化镍、硅化钼、硅化铂等。

电阻率与形成的温度是衡量salicide优劣的两项重要指标,电阻率越小,器件的性能就越好;温度越低,对已经形成的MOSFET性能影响就越小。表5-9列出了几类常见的Salicide的电阻率和形成温度。

表5-9 金属硅化物(salicides)的电阻与形成的温度范围

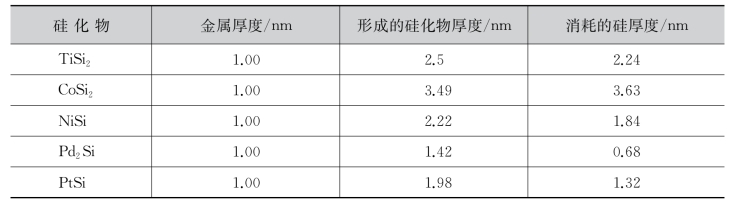

当淀积的金属层形成硅化层时,将消耗基底的部分Si材料。如表5-10所示,每淀积一单位厚度的金属钛,会消耗掉2.24单位厚度的硅,并形成2.5单位厚度的TiSi2。对CoSi2而言,每淀积一单位厚度的Co,会消耗掉3.63单位厚度的Si,形成3.49单位厚度的CoSi2。对于制造浅结MOSFET,源漏极Si的消耗是必须要考虑的一个因素。

表5-10 各种硅化物形成所消耗硅基层厚度值

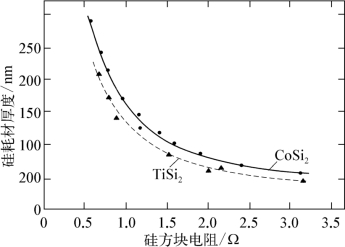

TiSi2虽然在所有硅材料中应用最广,然而当多晶硅栅极线宽缩小到0.5μm以下时,TiSi无法在狭窄的栅极上形成高导电性的C54相,从而使栅极的导电性较差。CoSi2虽然没有类似效应,然而CoSi2不能还原SiO2,所以事先需要对Si晶片进行必需的清洗。如图5-91所示,要得到相同的方块电阻,CoSi2需要消耗较厚的硅基底,这也使浅结面的形成比TiSi2更受限制。

图5-91 硅化物形成时所需消耗硅材与方块电阻的关系

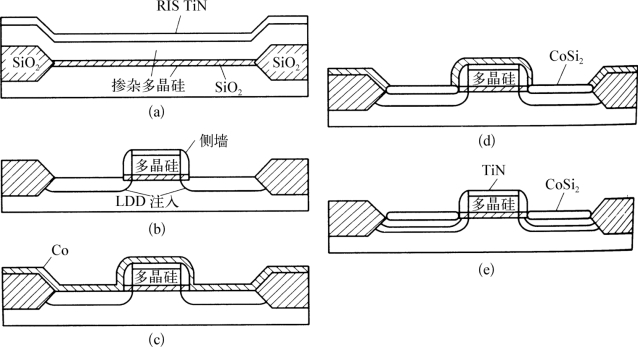

此外,一些掺杂物在CoSi2中扩散速度很快,因此在用p+多晶硅做P型晶体管栅极的亚0.25μm技术中,CoSi2若直接连接p+和n+多晶硅时,可使B离子扩散至N型多晶硅,使P离子扩散至P型多晶硅,造成多晶硅特性的漂移。可采用TiN/多晶硅的双层栅极来避免这一问题,如图5-92所示。

图5-92 TiN/Poly-Si的双层栅极结构

快速高温退火是应用于金属硅化物的形成的主要手段。在深亚微米器件制备工艺中,为避免源极/漏极的寄生串联电阻引起的晶体管驱动电流衰减,对源极/漏极区加以硅化处理已成为一种广为使用的技术。它可以由单纯源极/漏极区硅化处理或自行校准硅化处理来完成,自行校准硅化处理可同时实现源极/漏极和栅极区的硅化处理,对利用栅极作为导线的电路就更重要了。而随着器件尺寸的缩小,源极/漏极的结面变浅,所以源极/漏极的硅化层厚度也必须随之变薄,以避免形成漏电结面。举例来说,对0.18μm线宽的工艺技术,其结面深度小于0.1μm,而其源极/漏极硅化层的厚度可能只有0.01~0.04μm。

一般最常用的金属硅化层为TiSi2,其他如CoSi2、NiSi等近年来也有不少专家学者在研究。TiSi2的形成一般都采用两阶段退火方式,首先用溅射或CVD法生长一层金属钛膜,或采用共溅法溅射一层钛硅膜,接着在650℃左右进行第一阶段退火,使金属Ti与接触Si基板反应,形成TiSi2,此时的TiSi2主要由电阻率较高的C49相构成。使用溶液(例如去离子水∶30%双氧水∶NH4OH=5∶1∶1)除去淀积在绝缘层上未反应的金属Ti和反应过程中在表面形成的Si3N4层。接着在含H2或Ar2的气体中,在800℃左右进行第二阶段退火。第二阶段退火可将电阻值较高的C49相TiSi2转变为电阻率较低的C54相TiSi2,得到较低的方块电阻。如表5-11所示,金属Si化层的方块电阻值取决于淀积金属厚度、退火温度、时间及气氛(Ar或N2)。

表5-11 硅化钛方块电阻与工艺参数(金属钛厚、退火方式及温度时间)的关系

传统高温炉工艺不可避免的长热预算造成杂质扩散及接触面变深,将严重影响晶体管的特性,如穿通和,阀值电压降低等,使器件尺寸难以缩小。而对自对准硅化处理工艺,传统的高温炉退火方式容易造成源极、漏极和栅极间的短路,这是因为源极、漏极和栅极的TiSi2之间仅由薄壁空间隔离。更为主要的是,随着TiSi2变薄,所需的退火反应时间反而需要变长,而与短热损耗的目的背道而驰。这些因素均显示在深亚微米器件制备过程中,必须采用快速加热处理工艺。

3.反扩散层、黏结层

如果使铜互联线在集成电路有效应用,必须使用扩散阻挡层,在金属硅化物和连接金属Cu、Al之间加一层过渡层,用于防止金属(尤其是Cu)与隔离层及其硅之间相互扩散而造成的半导体器件性能的迁移,另外,也要防止金属Cu透过ILD(inter layer dielectctric)对地下的期间层造成污染。Cu在温度很低的情况下也能迅速在Si和SiO2中扩散,而且Cu与Si的结合力很差。Cu扩散进入Si和SiO2中会影响器件的少数载流子寿命和结的漏电流,引起设备性能变坏,可靠性下降。已经证明即使Cu含量非常低的情况下,设备的电性能也会降低。当电子设备变得越来越小时,阻挡层材料起着更为关键的作用,因此在铜互连集成电路中,阻挡层材料的选择以及阻挡层微结构在保护工作器件免受铜毒害方面的作用变得越来越重要。大多数研究集中在各种高熔点的纯金属Cr、Ti、Nb、Mo、Ta、W,和化合物(如TiN),利用从电阻值的增加和用二次离子质谱探测Si中的Cu,证实在难熔金属中Ta和W是比较优良的扩散阻挡层。人们也研究了高熔点的氮化物TiN、TaN、MoN和WN,证实它们也是有效的阻挡层。为了达到阻挡扩散的效果,孔洞底部的TiN必须有足够的厚度。一般使用的TiN阻隔层的厚度在80~120 nm之间。然而,在深宽比远大于1μm和洞口尺寸小于0.5μm时,传统溅射TiN的底部覆盖率不足,使用准直器可以有效地提升底部覆盖率,维持合理的工艺窗口。但在孔洞的口径持续降低的情况下,改善阻隔层的淀积技术就成为非常重要的研究内容,通常会采用ALD技术。

此外,由于Al金属或铝合金的表面强反射系数会对光刻工艺带来一定的不利影响,有必要在金属Al导线的表面制造一层防反光层,钛钨合金或TiN的薄膜都是很好的防反光层。同时,根据可靠性试验,以阻隔层上下夹住铝合金的导体连线,比单层铝合金连线的可靠性明显增加。综合阻绝作用、抗反射能力与可靠性的加强,多层(例如Ti/TiN/Al-Cu/TiN)导体连线技术已经取代传统的单层金属(如Al-Si-Cu)连线,成为亚微米器件中连线技术的主流。

集成电路工艺中常用的阻隔层有TiW合金及TiN两类,目前工业上最常用的扩散阻挡层材料为TiN。TiW合金可以与Si形成高浓度的合金,Si原子亦就不易穿过TiW层;TiN则以隔绝Si的扩散达到阻隔作用。TiN由于具有独特的物理及化学性质,正在成为VLSI金属化工艺中多种功能的一种导体材料。TiN可以有效地阻止Cu,Al与Si相互扩散。它与SiO2,Cu,Al等都有良好的牯附性。TiN作为Al、Cu、W的位障金属,阻止上下层材料之间的相互扩散,以增强器件的热稳定度和可靠性,因而在多层布线中又可作为多层薄膜之间的黏附层,衬垫层等。TiN在很广的光谱范围具有较低的反射率,约为Si的10~15倍,因此还可用做多层金属结构的表面抗反射层,以提高光刻精度。TiN层覆盖可抑制Al膜丘粒产生,有利于表面平整,提高抗电迁移性能。与W等其他材料构成复合金属结构时,利用刻蚀速率差别,TiN有时可起刻蚀自动终止的终点控制作用,TiN还可用作局部互连、垂直连接插塞(plug)等。

综上所述,过渡层X需要满足如下特性:

①两种材料经由X的穿透速率小;

②材料X对于材料A和B具有良好的热稳定性;

③材料X与材料A和B具有良好的黏着性;

④材料X与材料A和B的接触电阻小;

⑤材料X在厚度与结构上是均一的;

⑥多层膜体系AXB的热应力和机械应力较小;

⑦多层膜体系AXB的导热性和导电性好。

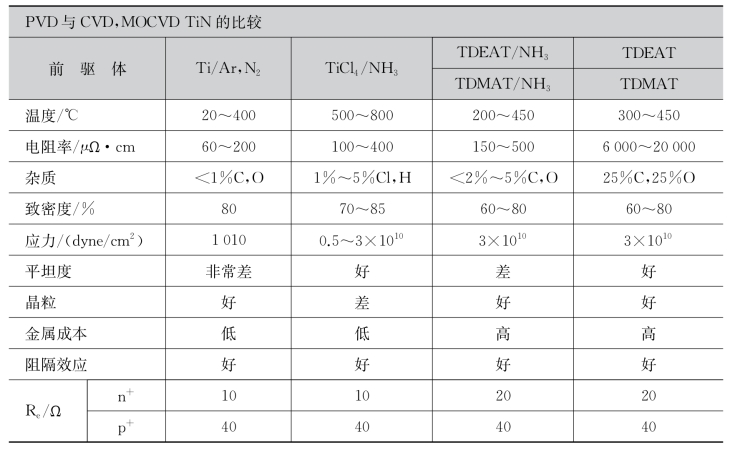

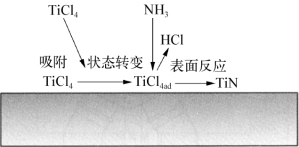

4.PVD与CVD,MOCVD TiN的比较

表5-12 PVD与CVD和MOCVD方法TiN之间的比较

如表5-12所示,常用TiN薄膜制备有物理气相淀积(PVD)工艺,化学气相淀积(CVD)工艺,化学镀淀积(ELD)工艺和原子层淀积(ALD)工艺。下面分别进行叙述。

(1)PVD方法。传统TiN的制造方法为PVD。目前,PVD生长TiN方式是以溅射法为主。在超高真空的环境下通入Ar,将Ti从金属靶中以溅射的方式击出,同时通入N2在晶片上形成TiN薄膜,这一过程称为活性离子溅射(RIS)。用反应离子溅射生长的TiN具有良好的薄膜特性,不仅可以作为扩散的阻隔层,也可覆盖在铝合金的上方作为防反光层。使用准直器辅助TiN的溅射,可显著地改善薄膜的阶梯覆盖性。

随着电子产品集成度的增加,接触孔的尺寸逐年降低,高宽比逐年提高,接触孔底部的覆盖率快速下降。为了阻止Al或F扩散到基底区,接触孔底部的TiN必须保持一定的厚度。这样,在接触孔周围上方氧化层处的TiN厚度需要增加2~3倍,但随之而来的是,在接触孔上方将形成突悬,如图5-93所示,会影响后续工艺中Al或W的填入。随着在孔洞尺寸逐年缩小,深宽比逐年提升,孔洞底部的覆盖率快速下降,准直器的使用将不具有生命力。溅射技术在大的深宽比下造成覆盖率下降和产生悬臂的原因是因为PVD过程中,反应物原子的黏滞系数大,原子自靶材表面溅射出来的角度为余弦分布。为了解决这一问题,在靶材与晶片之间加入了准直器,可以控制溅射出的原子到达晶片表面的入射角度分布,改进孔洞底部的覆盖率。然而采用这种方法,具有较大的缺点:有将近80%~90%的材料损失在准直器上,导致镀膜效率降低,靶材更换频率提高;另外,准直器洞口会逐渐缩小,造成准直器的更换频率较高。因此,在深宽比持续提升的情况下,选择更有效的Ti薄膜的淀积技术,实现黏着层的功能是目前产业界重要的工艺研发工作之一。

图5-93 非保角覆盖(non-conformal)薄膜在接触孔或介层洞顶端引起突变,导致锁孔洞的产生

(2)CVD方法。覆盖率是PVD技术不可避免的问题。因此,有人提出用CVD改善PVD所面临的问题。CVD TiN的覆盖率可维持在75%以上,但在导电性方面,CVD方式得到的金属内含有较多的杂质,电阻率则远大于溅射的金属材料。如果将薄膜进行适当的退火处理,则可有效降低薄膜电阻率2倍左右。退火时必须小心控制工艺的条件与温度,如在NH3为2.6 MPa的压强下退火2 min,即可达到降低薄膜电阻率的效果,而其他气体如N2、Ar与H2就无法在短时间内得到退火效应。LPCVD制备薄膜需要600℃以上的淀积或退火温度,才能得到较理想的薄膜特性。但在第一层金属导体连线完成后,工艺需维持在550℃以下。采用PECVD可以在保持相同的覆盖率效果的条件下,使TiN的淀积温度降至400℃以下。

根据所使用的含Ti反应气体的种类,CVD TiN可分为无机与有机两种。无机TiN的反应气体前驱体主要是TiCl4,有机TiN的反应气体前驱体一般较常用的有Ti[N(CH3)2]和Ti[N(C2H5)2],简写分别为TDMAT与TDEAT。这两种有机前驱体都含有金属Ti和有机官能团(CH3,或C2H5),将使用TDMAT或TDEAT作为前驱体的CVD方法也称为有机金属化学气相淀积(MOCVD)。以TiCl4为前驱体时的淀积温度较高,且伴随生成的微粒较多,但其原料较便宜、薄膜的阻值在可接受的范围内。以MOCVD为前驱体与NH3气体反应生成TiN薄膜的方法虽可降低薄膜的阻值,但其阶梯覆盖性会变得较差。下面分别进行叙述。

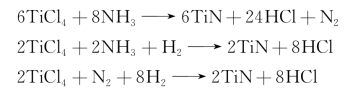

利用TiCl4作为反应气体,可以与NH3、H2/N2或NH3/N2反应形成TiN,其反应方程式分别为

图5-94 TiCl4/NH3的反应模型(https://www.xing528.com)

一般接触孔高温制程是采用(LPCVD)直接加热反应生成所需的TiN,而TiCl4/NH3与TiCl4/N2最大的差异是淀积的温度不同。TiCl4/NH3反应的温度约为400~700℃,而TiCl4/N2反应温度大于700℃,这是因为N2是一个惰性较大的气体,不易分解出氮原子与TiCl4反应生成TiN。因为TiCl4/N2的LPCVDTiN工艺的温度过高,所以大部分的LPCVD TiN都采用TiCl4/NH,作为反应气体。其反应模型如图5-94所示,TiCl4先扩散、吸附到热的晶片上,然后NH3直接与吸附在晶片上的TiCl4反应生成TiN与HCl,HCl成为气体被抽走。

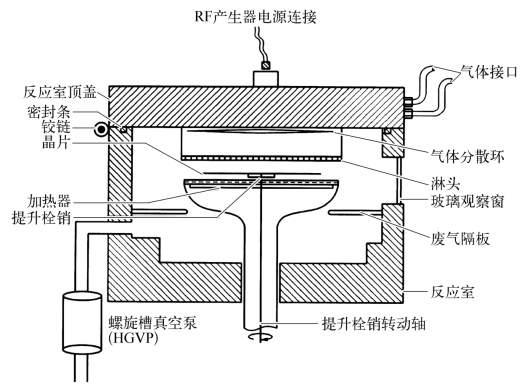

下面以MRC公司的Phoenix CVD Ti/TiN系统为例说明TiN设备的结构。其是以TiCl4作为主要反应气体,该系统包含了七个真空腔,如图5-95所示。

图5-95 金属CVD系统

晶片先由VEC(抽真空)腔传到SSE(溅射刻蚀)腔,对晶片进行预清洗,利用低能量的Ar离子去除晶片表面的氧化物或污染物。SSE腔的构造如图5-96所示,它具有一个RF产生器,上半部利用450 kHz的射频产生等离子体,下基板接上另一个13.5 MHz的射频源以控制Ar离子的能量。晶片经过Ar离子的预清洗后,直接送到TiN腔淀积TiN。TiN的反应气体是TiCl4与NH3,而Ti的反应气体为TiCl4与H2。

图5-96 SSE反应腔的结构

因为Ti有极高的电负性,所以无法直接用加热的方式将Ti由TiCl4中还原出来,需采用等离子体辅助的方式才能淀积制备Ti薄膜。另外一方面,由于Si基板的温度约为650℃,所以淀积的Ti会与基底反应生成TiSi2。这两种反应的方程式分别为

TiSi2的形成可以确保Ti与硅间较低的接触电阻。利用TiCl4作为反应气体,另一个最大的好处就是它可以同时淀积Ti与TiN,使这二种薄膜可以在同一个淀积室或同一个系统内的不同淀积室内制备。这一特色可以促进薄膜制备工艺的整合。TiN虽是一个很好的位障金属,但与Si的接触电阻极大,所以TiN与Si间需有一层Ti薄膜以确保较低的接触电阻。而使用MOCVD制备TiN的工艺中,因为不能淀积Ti膜,所以需先用PVD系统淀积Ti,再将晶片拿出来放入MOCVD淀积TiN。

在Phoenix系统中,TiN与Ti的反应腔结构完全相同。其构造如图5-97所示,是通过基板背面的热阻丝加热,反应气体通过反应器上端的气体分散环与淋头进入反应器,由此可得到均匀的气体分布。另外,在反应器上端有一个RF生产器,因为在淀积Ti时,需要等离子体辅助淀积。在淀积TiN时,一般不用等离子体辅助淀积,而是采用LPCVD的方式,反应温度为600~650℃,因此可以得到极佳的保角覆盖。

图5-97 CVD TiN与CVD Ti的反应室

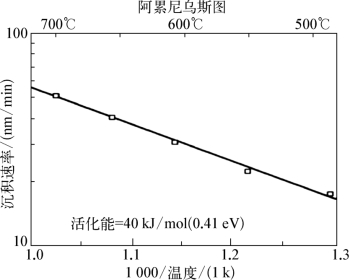

图5-98 低压CVD TiN镀膜速率与温度的关系

但是,想要降低淀积温度,就要使用等离子体辅助淀积,这对Al走线孔相当重要。图5-98为TiN的淀积速率与淀积温度的关系图。由图可知,反应的活化能为0.41 eV。一般而言,化学活化能大于0.25 eV的反应,其机制为表面反应限制,因此采用这种化学反应镀膜能有百分之百的覆盖率。

上面所述的CVD Ti/TiN的淀积温度为600~650℃,比较适合用于接触孔处薄膜的淀积;若要用在金属导体互连线结构中的铝走线孔中,温度必须小于或等于400℃。可以采用等离子体辅助的方式来降低淀积温度。若以纯加热的方式来淀积TiN膜,其阻值会随着温度的下降而急剧上升,这是由于温度过低时,TiCl4的分解反应不够完全,使TiN中含有太多的Cl,从而造成电阻值变高;此外,Cl含量过高也会造成对Al导线的腐蚀,所以热CVD无法在400℃长出适合的TiN膜。此时若采用PECVD的方式,则可使TiCl4中的Cl有效地分解,让TiCl4与NH3的反应非常完全,所以在400℃的淀积温度下也可得到电阻值与Cl含量都非常小的TiN膜。但是,使用PECVD技术将会使阶梯覆盖率变差,因为等离子体会造成反应气体在气相中发生反应。热CVD TiN与PECVD TiN的薄膜性质如表5-13所示。

表5-13 热CVD TiN与PECVD TiN的薄膜性质比较

5.电子回旋共振化学气相淀积(ECR-CVD)Ti/TiN

图5-99 ECR-CVD的结构

用TiCl4/NH3反应制备TiN薄膜时,容易形成TiCl4×NH3,造成微尘来源。而采用TiCl4/N2则不会出现这一缺点。但是,因为N2是一极具惰性的气体,所以反应温度极高(>700℃),不适合用在IC制造工艺中。目前Sumitomo公司提出了高等离子体密度ECRCVD的方式,可在低温下(300~400℃)利用TiCl4/H2与TiCl4/N2淀积Ti与TiN。在低温下淀积的原因是ECR-CVD可以产生高密度的等离子体,使反应气体可以完全分解并反应。ECR-CVD的结构如图5-99所示,主要的结构是一组电磁铁与微波产生器。电子在磁场中会做螺旋运动,其回旋频率ω=eB/m。其中B是外加磁场,e与m分别为电子的电荷和质量。当外加磁场B=0.0873 T时,电子的回旋频率ω=2.45 GHz,若此时从外界加入一个频率为2.45 GHz的电磁波,则电子就会获得电磁波的能量而形成共振,也就是说,这时的电子将具有极大的动能,凡是被其撞击的气体分子都极易被解离形成等离子体;另外,由于外加磁场使电子作回旋运动,增加了电子与反应气体分子的碰撞概率。因此,ECR-CVD可以产生高密度的等离子体。

表5-14为传统RF与ECR产生等离子体的比较。由表可知,ECR产生的等离子体的密度约为1E10~1E12 ions/cm3,是传统RF等离子体密度的10~100倍;就分解率而言,ECR是传统RF的1000倍。在如图5-99所示的结构中,通过微波的石英窗口加有一个RF偏压,这是因为薄膜淀积时,CVD Ti或TiN金属膜会淀积在此石英窗口使微波无法进入等离子体腔,造成ECR等离子体无法维持。加RF偏压后,可利用Ar离子去除石英窗口的Ti或TiN,使微波能进入离子腔室以维持稳定的等离子体密度。

表5-14 传统RF与ECR产生等离子体的比较

图5-100是采用ECR-CVD法在300℃淀积的Ti/TiN(20 nm/100 nm)经750℃20秒快速退火前后的X射线衍射图。可以发现,300℃的ECR-CVD TiN具有〈200〉的优选方向,这与TiCl4/NH4反应得到的TiN相同。经750℃20秒的快速退火后,Ti会与Si基底形成C49相的TiSi2。

图5-100 300℃淀积的Ti/TiN(20 nm/100 nm)在750℃20 min快速退火前后的X射线衍射图

6.MOCVD TiN(有机金属化学气相淀积)

在PVD过程中,反应物原子的黏滞系数大,为了解决这一问题,在靶材与晶片之间加入了准直器,改进了孔洞底部的覆盖率。然而采用这种方法,具有较大的缺点:将有近80%~90%的材料损失在准直器上,导致镀膜效率降低,靶材更换频率提高。另外,准直器洞口会逐渐缩小,造成准直器的更换频率较高。这些都是PVD技术不可避免的问题,因此,有人提出用CVD改善PVD所面临的问题。根据所使用的含Ti反应气体的种类,CVD方法制备TiN薄膜的原料分无机和有机两大类,有机类用TDMAT及TDEAT(四双乙基胺钛)提供Ti金属的原子,这就是MOCVD的方法。

使用有机金属作为前驱体淀积TiN薄膜的最大优点是淀积温度可低于450℃,因此就可应用在管洞的填充上。一般,较常使用的有机金属前驱物有TDEAT[Ti(NEt2)4]、TDMAT[Ti(NMe2)4]和最新的TEMAT[TiN(CH3)C2H5]。其他的有机金属前驱体还有:C,2Ti(N)2、TiCl2(NH2tBu)2(NH2tBu)0~2等。利用MOCVD热解淀积TiN薄膜可分为TDEAT/TDMAT和TDEAT+NH/TDMAT+NH3两大类。因为TDEAT和TDMAT二者本身就含有氮原子,直接热解时虽可生成TiN薄膜并具有很好的阶梯覆盖性,但是所需的淀积温度过高,且形成的薄膜具有多孔性,并常含有大量的C,易迅速捕捉大气中的O。因此,直接热解制备的TiN薄膜将具有相当高的电阻率(6000~20000μΩ·cm),而且阻率会随着暴露在大气中时间的增加而上升。若反应时加入NH,气体,不仅可降低淀积温度,还可减少TiN薄膜中C和O的含量。另外,在较高的NH,流速下生长的薄膜比较致密并有较低的电阻率(150~500μΩ·cm),但是具有较差的阶梯覆盖性,会影响对管洞和接触孔的填充。下面的讨论将以现今一般所常用的TDEAT和TDMAT为主再加上最新的TEMAT前驱体。

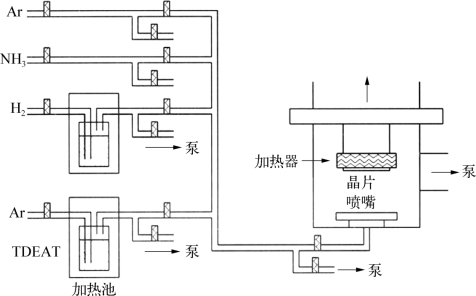

图5-101是常见MOCVD淀积设备,是一种冷壁式(cold-wall)低压反应器,淀积薄膜前反应器的压力低于1E-3Pa。分别以上述的前驱体(如TDEAT、TDMAT和TEMAT)和NH3作为反应气体。TDEAT与TDMAT的主要差别在于TDEAT的闪点为10℃,具有较高的危险性。此外,因为TDMAT的蒸气压较高,所以使用TDMAT时薄膜淀积速率比TDEAT快,TEMAT则介于两者之间。TDEAT、TDMAT和TEMAT三者的蒸气压在约80℃时分别为8 Pa、266 Pa和133 Pa。三者的颜色分别是淡黄色、暗黄色与橘黄色。

图5-101 MOCVD系统结构

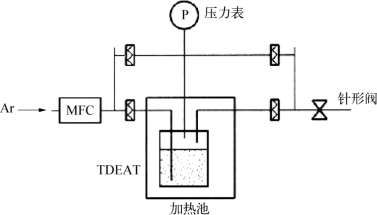

因为TDEAT、TDMAT和TEMAT三种前驱体在常温常压下为液态,所以须采用较为昂贵的传送方式来传送前驱体。一般是先将前驱体加热到40~100℃,再用高纯度Ar气作为载气运送加热起泡后的液态前驱体进入反应室内与NH3进行反应。图5-102、图5-103是前驱体传送系统与TDEAT、TDMAT和TiCl4的蒸气压与温度的关系图。

图5-102 气泡系统结构

图5-103 TDEAT、TDMAT和TiCl4蒸气压与温度之间的关系

TDEAT、TDMAT与NH3反应生成TiN薄膜的反应方程式可表示为

![]()

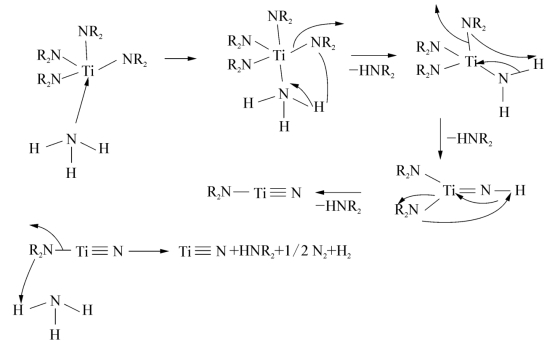

式中,R为—CH2、—C2H5或—CH3C2H5。这三者的反应机理也很相似,以TDMAT为例,反应机理如图5-104所示。

图5-104 TDMAT与NH3的反应机理

若无NH,气体、仅利用热解法淀积TiN膜时的可能的反应机理如图5-105所示。

图5-105 经过热解产生TiN的反应机理

实验发现,当淀积温度为250~350℃时,使用TEMAT前驱体可使TiN薄膜中的C含量下降到18%,其电阻率约为2500μΩ·cm,但TDEAT热解生成的TiN薄膜的C含量为30%,电阻率为6000μΩ·cm以上。Raajmakers和Sherman研究发现,TiN薄膜中含有C和O杂质对电阻的影响比Cl杂质的影响大。在TDEAr(或TDMAT)和NH3的反应系统中,高压或高NH3流速会促进TDEAT(或TDMAr)和NH3的气相反应,得到较致密的薄膜,使薄膜在大气中不易吸收O,可得到电阻率较低的薄膜。但是,高压或高NH3流速会造成阶梯覆盖性下降而影响该工艺在器件制造中的应用。反之,在低压或低NH3流速下所形成的TiN薄膜具有较高的阻值,薄膜较为疏松,在大气下很容易吸收O,使薄膜的阻值随着暴露在大气中时间的增加而增大。此外,在较高的温度下,反应倾向扩散限制,导致较差的阶梯覆盖性;在低温时,反应为表面限制反应,能提供良好的阶梯覆盖性。

最近几年,世界各地的研究室纷纷尝试解决MOCVD TiN薄膜中C和O含量高的缺点。在此,列举几个比较重要的改善MOCVD TiN薄膜性能的方法:

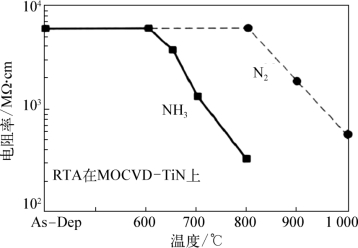

图5-106 不同气氛下TiN薄膜电阻率与RTA温度的关系

利用快速热退火(RTA)的方式,因其导入气体为NH3,故简称RTN。图5-106是以TDMAT为例,比较通入N2与通入NH3时RTA对TiN薄膜电阻率影响的差异。由图5-106可知,经过800℃的RTN处理后,电阻率由未处理时的6000μΩ·cm(见图中As-Dep所对应的点)可大幅下降到320μΩ·cm。因此,进行RTN处理对仅利用热解方式制备高C和O含量TiN薄膜的工艺提供了一个既能降低阻值又兼具薄膜均匀性的新途径,但这种工艺因处理温度过高,仅适用于接触孔的制作工艺。

利用N2等离子体法,可降低阻值、C和O的含量。以TDMAT为例,通过N2等离子体法处理的MOCVD TiN薄膜暴露在大气下,其阻值并不会急剧上升,且C含量由30%降低到23%,成为优良的TiN薄膜。因此,利用N2等离子体法对TiN薄膜进行改善,也是一种新的方法。

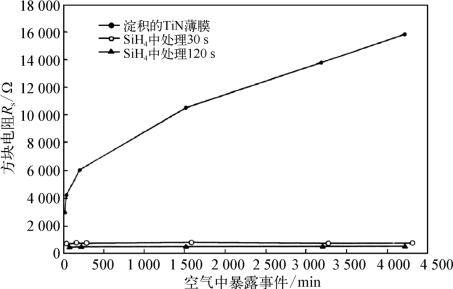

利用SiH4气体提升MOCVD TiN薄膜的稳定性与均匀性。图5-107表明经过SiH4处理后,暴露在大气下的薄膜的电阻率并不会明显上升。因此,处理过的TiN薄膜的性质也可获得明显提升。

图5-107 经过SiH4处理和未经过处理的TiN薄膜电阻与空气中暴露事件的关系比较

7.ALD TiN

ALD相比传统的CVD和PVD等淀积工艺具有先天的优势:它充分利用表面自限制饱和反应(self-limiting surface saturation reactions),具有厚度精确控制和高的稳定性,对温度和反应先体通量的变化不太敏感,这样得到的薄膜具有低电阻率、低杂质浓度、均匀致密等特性,且在深宽比高达100∶1的结构也可实现良好的台阶覆盖率(step coverage),后者在制作铜互连纳米级接触孔方面非常重要。如图5-108所示,常规的PLD方法无法达到均匀的薄膜覆盖,会产生空洞的效应,而ALD就可以达到很均匀的阶梯薄膜覆盖。

图5-108 ALD优越的覆盖能力示意

注:集成电路中铜金属互连层需要用TiN或TaN作为隔离缓冲层,厚度大概在几纳米左右。接触孔与互连层之间的互连孔也只有几十个纳米的孔径,在如此狭小的区域使用普通的PVD方法无法得到可靠的孔内隔离层填充,而使用ALD的精细加工,可以得到很好地平台与夹角薄膜覆盖。好在缓冲隔离层的厚度只有几纳米,薄膜点击的生产效率不会受到过多的影响。

已经开展了大量的用ALD制作的TiN扩散阻挡层薄膜的研究。J.Y.Kim等在Cu/TiN/SiO2/Si系统里以TDMAT为先体,分别利用H2,N2/H2,N2,等离子体增强原子层淀积得到了低杂质浓度、低电阻率(300Ωcm)、高台阶覆盖率(95%)和保形性好的TiN扩散阻挡层。研究表明,用N2等离子体增强原子层淀积得到杂质浓度最低,电阻率也最低。J.Mussehoot等以TDMAT为先体,分别利用N2,NH3以及N2,NH3等离子体增强ALD TiN薄膜,并比较了热原子层淀积与等离子体增强原子层淀积薄膜的阻挡特性等,最终得到了杂质浓度低于6%,电阻率最低180Ωcm的TiN扩散阻挡层,并研究了等离子体功率、时间、温度对阻挡层性质的影响。

目前,扩散阻挡层的研究还是主要集中在三个方面:材料选择,制备工艺的改进,薄膜的处理。TiN作为阻挡层材料,具有高的稳定性和低电阻率等优势,ALD由于基于自限制饱和吸附反应,成为一种最有希望的薄膜淀积工艺。所以,未来对ALD TiN的研究还是十分重要的。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。