1.快速加热工艺技术

快速加热工艺(rapid thermal processing,RTP)为近年来颇受瞩目的一项新技术,并已开始被广泛应用于超大规模集成电路的制造,来取代传统高温灯管。传统式高温灯管的缺点是在加热过程中,前后需要很长的升热和降热时间(其升热降热速率约为5~50℃/min),造成无可避免长热预算时间,引起掺杂浓度及结合面的扩散,因此已无法满足深亚微米元件工艺的低热预算需求。而快速加热工艺因利用瞬时光管(transient lamp)快速加热的原理,可在很短的几秒钟时间内(其升温和降温速率可达10~200℃/s),将一整片硅晶片加热到几百度甚至一千度以上高温,符合深亚微米元件工艺的低热预算需求,故近年来已有取代传统灯管的趋势。快速加热工艺的可能应用范围很广,包括超薄氧化层生长,氮氧化层生长,退火,扩散,金属硅化物形成,浅接面形成等等,适合大量生产的RTA机器设备在1992年趋于成熟。将于本章中分别详述。

传统高温灯管工艺是利用对热流和热传导的加热原理,使硅晶片与整个灯管周围环境达到热平衡,因此可非常精确地控制晶片上的实际温度,且可一次同时加热大量的晶片,很适合传统的多晶片制备(batch process),而达到降低制备时间及成本的目的。然而其最大的缺点为升热预算,使其无法胜任深亚微米元件工艺的应用。且因为灯管壁长时间被加热到高温,容易淀积杂质,使晶片遭受污染。因此随着元件的缩小,传统高温灯管制备越来越难满足对污染的严格要求。而快速加热制备因利用瞬时光管的快速加热,及只对硅晶片选择性吸热的特殊性,可以迅速将晶片选择性升温,而使周围腔壁仍维持在低温;不但减低热预算,且减少晶片污染,很适合八寸及未来更大直径晶片的单片(single wafer)制备。

快速加热制备的缺点则为较难准确控制晶片的实际温度及其均匀性,而且也有可能在晶片上产生瞬间大量的不均匀温度分布,进而引发位错等晶片缺陷。这是因为快速加热制备是利用瞬间光管对硅晶片选择性吸热的原理,所以实际晶片的升温速率取决于很多复杂的因素,包括晶片本身的吸热效率,瞬时光管辐射的波长及强度,RTP周围腔壁的反射率,以及辐射光的反射及折射。晶片本身的吸收效率取决于起始晶片本身的放射特性(intrinsic emissivity),以及所有淀积或成长于晶片表面或背面的绝缘层或导电层的外加放射特性(extrinsic emissivity)。而对一有实际电路图形的晶片,其情形更为复杂。因为线路图形造成晶片表明分布状况的不同,可引起一片晶片上不均匀的温度分布。一般而言,对1.2~6μm的光管辐射波长及600度以下的温度,硅晶片的升温速率主要是取决于晶片的本身放射特性;因此其升温速率受晶片厚度、杂质浓度的影响。如何设计出能减缓晶片上不均匀升温的快速加热系统,是所有RTP设备制造厂的一个最主要研发项目。

如上所述,在同一晶片上温度的均匀性,是快速加热制备设备很重要的一个指标。一个简易测定快速加热制备中晶片上的温度分布的方式,是在空白硅晶片上,以不同的时间及温度生长氧化层。再以椭圆测厚仪法测量氧化层厚度,根据氧化机制中厚度与温度的关系方程式,即可换算出晶片上的温度分布。为了减轻晶片上不均匀的升温现象,可用大面积分布的热源代替早期的单一点状热源,使晶片升温更为均匀。而且因为考虑晶片周围散热较快的因素,一般可在晶片周围加以加大的热源,或者尽量减少晶片的散热,来达到减小晶片上的温差的效果。对1050~1150℃间的制备温度,一般商用制备设备的晶片温差大约可控制在±15℃之内。在此温度范围内,SUPREM模拟结果显示对结合面深度可产生约7%的差异。

一般常用瞬时光管辐射源有钨卤灯、氙灯、氩灯等。瞬时光管之所以能对硅晶片作选择性升温,是因为一般所用的光源波长在0.3~4μm之间,石英管壁无法有效吸收此段波长的辐射,而硅晶片则恰好相反。光源的能量几乎全部用来做加热晶片用,故可以在短短的数秒钟内,很快将晶片升温至制备所需的温度。而石英管壁则仍维持在低温,是属于所谓的冷壁(cold wall)制备。

几乎所有商用RTP设备都利用红外线高温计测法(infrared optical pyromatry)来量测制备当中晶片温度。红外线高温计提供了一个快速,无接触的温度测量方式。然而红外线高温计的最大缺陷,是硅晶片的放射性特性为一相当难的函数,受很多因素的影响;其中包括所有淀积或成长于晶片表面及背面的各种绝缘层或导电层,以及硅晶片上的线路图形。所以在实际生产时,须针对每一片晶片作个别校正,才能保证制备温度的精确性及复杂性。而为了增进温度测量的精确度,通常可采用整合温度控制系统。

集成电路制备过程中,需要将晶片加热的步骤包括快速加热化学氧化淀积(RTCVD)、超薄氧化层成长及氮化、注入离子活化、浅接合而形成、退火、扩散、金属硅化物形成、垒晶生长、双极元件中浅掺杂晶体射极成长,以及接触孔铝合金形成等等。以下将分别叙述快速加热制备过程在上述步骤中的应用。

2.快速加热化学气相淀积(RT-CVD,rapid thermal-CVD)

一般低压化学气相淀积(LPCVD)制备过程,在0.5 torr的气压中淀积薄膜。在这个压力范围内,主要的传热方式为热传导。而对流为次要因素,而且对600℃以上的制备过程,硅晶片的热辐射源是不透明的;换句话说,热辐射源的热被晶片表面吸收。辐射热损失也将发生在晶片表面。

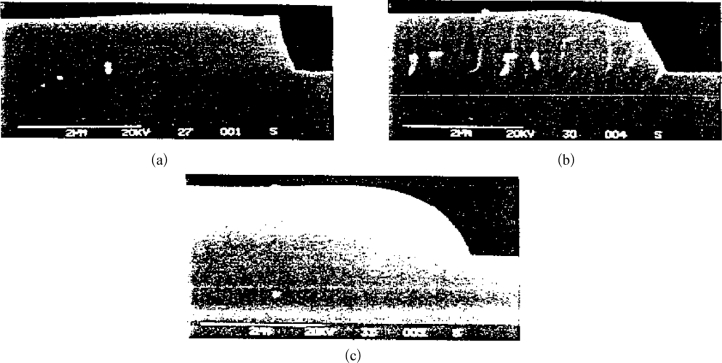

传统LPCVD通常是多片制备过程(batch process),一次可同时淀积几十片晶片,因此可以容忍较慢的淀积率(Å/min)。而RTP制备过程,较适合采用单片制备过程,因此应用到CVD制备过程时,必须考虑以提高制备温度,来获得较高的淀积率(大于1000Å/min),才能维持30~60片/h晶片的合理量产输出率。如图7-36所示,以SiH4成长作为栅极的多晶硅时,若将RTP制备过程温度提高到725℃,则淀积率可提高到1000Å/min以上。与采用625℃左右的传统LPCVD制备过程比较,其淀积率大约快了10倍,故勉强可弥补单片制备方式先天上较慢的输出率。对传统的LPCVD制备过程,提高制备过程温度通常都会无可避免地形成表面粗糙的多晶硅;然而对RT-CVD法,若采用较高的制备过程气压(约3~4 torr),可得到表面相当平滑的多晶硅,如图7-37所示。

图7-36 以RTP法生长多晶硅淀积率与温度关系

图7-37 以RTP法生长多晶硅表面粗度与制程气压关系

注:当气压大于3 torr以上时,可得表面相当平滑的多晶硅。

RT-CVD除了应用于多晶硅外,也可用来淀积二氧化硅及氧化硅。对传统LPCVD方法,SiH2Cl2或是SiH4均可用来淀积氮化硅。然而在考虑如何应用到RT-CVD制备过程时,因为SiH2Cl2制备过程会产生氯化氨(NH4Cl)副产品,会大量淀积于包括管壁与石英窗在内的整个RT-CVD系统;因此以RT-CVD淀积氮化硅时,通常均采用NH3∶SiH4的比例应大于120∶1才能获得正确化学成分比(tachometric)的氮化硅。可是对如此高的NH3∶SiH4比,即使在785℃的高温环境下,氮化硅淀积率仍然非常慢(100Å/s)如图7-38所示。因此RT-CVD制备过程通常只适合用来淀积可作栅极介电层用的薄氮化硅。

图7-38 以RTP法生长氮化硅淀积率与NH3::SiH4流量比的关系

RT-CVD法应用于需要厚氧化硅层(数千埃)的后续制备过程。例如,边壁间隔时,需要兼顾高淀积率及均覆性,因此通常采用TEOS(tetraethoxysilane or tetraethylorthosilicate),以800℃以上的高温,可得每分钟1000埃的淀积速率,符合单片制备过程大量生产输出率的要求。然而如此高的温度,却使其无法应用于多层金属导体连线间的绝缘层。截至目前为止,市场上尚无适合淀积多层金属连线的绝缘层低温(小于450℃)系统问世。

RT-CVD薄氧化硅层的优点在于可同时生长薄栅极介电层及栅极多晶硅。这是因为二者均可以RT-CVD法淀积,故可利用同一套多腔RT-CVD淀积系统,一气呵成,不需破坏真空度,使介面没有污染。此特点也是以RT-CVD淀积氧化硅的方式与下一节中将叙述的超薄氧化层生长法最大的不同之处。RTD一般是以950℃以上的高温,在大气压力下生长。虽然RTO法一般有较佳的特性,但却无法与以低气压淀积的多晶硅栅极共用一套多腔系统,在同一次抽真空中完成生长。要用RT-CVD法淀积薄栅极二氧化硅,可用SiH4及N2O,在800℃淀积。其活化能约为1.5~1.75 eV。淀积速率则可达50Å/min,此速率约为传统高温氧化法的100倍。

3.快速氧化层生长及氮化

快速氧化及氮化制备过程很适合用于生长深亚微米元件所需的超薄氧化层。一般而言,对0.25μm工艺,其氧化层厚度只在60~70Å。而对0.18μm工艺,其氧化层厚度只有40Å。一个理想的RTO系统除了具备一个理想的RTP的基本条件外,还需能够处理氧化过程所需的各种反应气体,且能够很快地变换工艺所需的气体,而不污染晶片。而且RTO系统也同时要能够抽真空。

RTO工艺可为单一阶段式,或是如图7-38所示之一典型两阶段RTO工艺。两阶段RTO工艺是在单一阶段式RTO之后,附加一段快速退火。如图7-39所示,RTO生长速率及活化能量并不同于RTO系统,其线性区的活化能量可在1.41~1.71之间;而传统高温灯管的值则约为1.76。如图7-40所示,RTO的氧化率在〈110〉方向最快,而在〈100〉方向最慢。而且不同方向的氧化率差别会随着RTO温度升高而降低。因此在1200℃的RTO温度,不同方向上几乎有着相同的成长速率。至于HCl对RTO的作用,则与传统高温氧化灯生长相似,均有提高氧化率的效果;如图7-41所示。以高浓度硅晶作基板,也同样有提高氧化率的效果。

图7-39 RTO生长速率与温度关系图

图7-40 RTO法生长速率与硅晶圆的关系

(a)950℃(b)1050℃(c)1200℃在高生长温度时,各方向间的速率差别减小

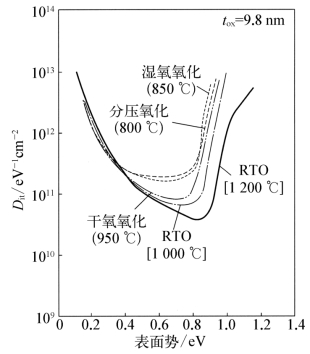

图7-41 RTO与传统灯管(FO)生长氧化层介面捕获密度分布比较

一般最常见RTO温度控制系统为开路式控制,利用高温计的测量值,作为控制回来输入。因此必须知道晶片的有效光放射特性,才能精确换算出晶片上的确切温度。然而如本章前面所述,晶片的有效光放射特性受很多因素所影响,导致精确度控制上的困难。一般而言,晶片实际温度测量值的误差可达50℃。

利用RTO生长超薄氧化层,一般均有极好的电特性。不论固定电荷,界面电荷,击穿总电荷等特性,均可与传统高温氧化灯生长相匹配,甚至更好。例如在一对照实验中,Qbd值可从传统高温氧化生长的20 Coulomb/cm2,显著增进至80 Coulomb/cm2。如图7-42所示,RTO所得介电层也有较好的界面捕获密度和零时介质崩溃电压的分布。这些实验数据均显示,快速生长法可得较好性能的氧化层。

图7-42 RTO与传统灯管(F0)生长氧化层击穿电压(TZDB)比较

(a)厚度75埃(b)厚度98埃,RTO法可得较佳的击穿电压

快速工艺也可用来对氧化层加以氮化,使形成一含氮的界面,而得到更好的电性能。氮化氧化层同时也可增进对硼渗透的抵抗力,对以P+型多晶硅作为P型晶体管栅极的次0.25μm技术,就更加重要了。各种不同的气体,包括NH3、N2O、NO等均曾被用来做TRN。NH3可形成含氮量高,对硼渗透有高阻抗的介电层,其缺点是使电子俘获率及载流子迁移率恶化。N2O的主要缺点为无法形成含氮高的界面,从而无法有效遏制硼渗透。NO生长有极好的电特性,同时也比N2O更有效使介面氮化,是一种极有潜力的新工艺。(https://www.xing528.com)

4.注入离子活化及浅接合面形成

随着MOS元件微缩,沟道的掺杂浓度及源极/漏极区接合面必须相对变浅,以避免短沟道效应。例如对0.18μm元件,其所需源极/漏极区接合面深度,可能只有0.07μm。而要保持0.07μm的p+/n接合面深度,根据工艺模拟软件PREDICT1.5的推算,其所能容忍最大热预算将不能大于1000℃/24 s2。更有甚者,用此软件算得的是最乐观的容许热预算值。对实际情况,尤其是低能量离子注入时,若考虑因粒子破坏所引起的暂态加速扩散,则实际所能容忍的热预算可能只有PREDICT推算值的十分之一。显而易见,对Gbit级以上的晶体管电路技术,其所需的浅接合面及陡而窄的掺杂浓度分布,已非传统高温灯管制备所能承担,而必须借助于快速加热工艺不可。

根据注入离子的种类及浓度,可在硅晶内产生各种不同的缺陷。例如当离子浓度大约小于2×1014cm2时,主要形成的是点缺陷或缺陷群。如图7-43(a)所示,间隙式缺陷(简称Ⅰ型)可分布在整个注入区,以及更深的晶体内部。但当离子浓度大于上述值时,此时硅晶体表面可形成一非晶层。如图7-43(b)所示,在非晶层部分形成空位型缺陷(简称Ⅴ型);而Ⅰ型缺陷则形成于非晶层下方。而位于非晶层及其下方晶层交界处则产生称为Type-Ⅱ的错位环。因为Type-Ⅱ错位环刚好位于离子注入纵向深度的终点,所以又称为注入终点缺陷(简称ERO缺陷)。

图7-43 B离子注入产生的三种缺陷及其分布

(a)低离子浓度时,Ⅰ型缺陷形成在整个分布区(b)离子浓度增加时Ⅴ型缺陷在非晶区形成Ⅰ型缺陷在非晶区下方形成(c)高离子浓度时,纵深缺陷很难用高温退火去除

另外一种缺陷主要发生于高浓度硼离子注入,称为纵深点缺陷,其形成的主要原因为在纵深点附近注入;离子因浓度超过固态溶解度而形成析出物。此种缺陷即使在1050℃的高温时,也相当稳定,因此很难用退火处理除去。一般在退火时,这种纵深点缺陷会演化成自间隙型缺陷,这种缺陷也是引起暂态加速扩散的主要原因。

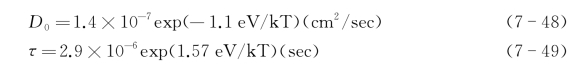

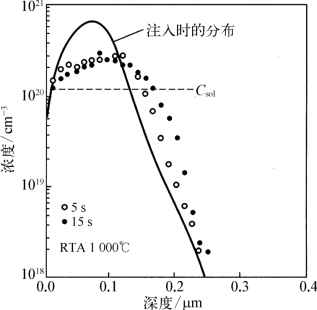

近年来对利用RTP工艺形成深亚微米元件所需注入离子活化,及n+/p,p+/n等浅接面均有很多文献,其中最显著讨论广的现象为暂态加速扩散。以低剂量硼离子为例,其暂态加速扩散时间常数D(t)为

其中Di为硼本身的扩散系数,D0为t=0时的加速扩散系数,τ为点状缺陷的衰减率,其关系如下

对低于1050℃极短的RTA,硼离子的暂态加速扩散速率,取决于点状缺陷群的快速衰减率。因此暂态加速扩散常数与损坏的时间常数,二者也是息息相关的。而在较高的温度时(>1050℃),硼离子的暂态加速扩散速率,则取决于Type-Ⅱ错位环的衰减率。一般而言,暂态加速扩散时间常数可随着注入剂量增加而变长。对1×1014cm2时,因晶格损坏的程度增大,使暂态加速扩散延长至40 s结束。在如此高的注入剂量时,在离子浓度的高峰点附近,形成一以缓慢速率扩散的区域;而在扩散点最前端的离子,则以上百倍的速率向前推进。从实用的角度来说,硼及磷离子在RTA处理时的暂态扩散现象,都可通过降低注入离子的能量来减轻。

比较可知硼的暂态扩散时间常数随注入浓度增加而延长硼离子的活化机制,取决于硼离子从间隙晶格位置进入取代性晶格位置。因为这过程牵扯到需要从由点状缺陷为中继站,所以活化能量为5 eV(此即硅原子的扩散能量),所以随温度的变化很强烈。高浓度注入的硼离子在低于850℃时,其活化速率非常缓慢。如图7-44所示,即使经过800℃,两小时退火,大多数的硼离子仍然尚未活化。相比之下,在摄氏900度以上的RTA温度,其活化效率则提高许多。如图7-45所示,对1×1016cm2的高剂量注入离子,在1000℃,5 s的RTA处理后,即可达到2×1015cm2高的活化离子浓度。

非活化的磷离子是以磷化物的形式存在,高温RTA处理很容易将磷离子完全活化,并无问题,而砷离子的活化机制与磷离子类似,虽然文献中对非活化砷离子的存在形式仍有争议。一般来说,对高浓度砷离子,1000℃,5 min的RTA;或是900℃,1 h,都可有效地将砷离子活化。

图7-44 高浓度注入(20 keV,2×1015cm-2)硼离子经800℃不同退火时间(5 min及2 h)活化载流子浓度纵深

图7-45 高浓度注入(30 keV,1×1016cm-2)的硼离子经900℃不同退火时间(5 s及15 s)活化载流子浓度纵深

5.金属硅化物形成

快速高温退火很可能普及所有后段工艺,然而RTP工艺中最成熟且最早应用于量产的工艺当首推金属硅化物的形成。在深亚微米元件工艺中,为避免源极/漏极区寄生串联电阻引起的晶体管驱动电流衰减,对源极/漏极区加以硅化处理,已成为一重要且广为应用的工艺技术。这可以由单纯源极/漏极区硅化处理或由自行校准硅化处理来完成。自行校准硅化处理可同时完成源极/漏极栅极区的硅化处理,对利用栅极作为导线的电路就更重要了。而随着元件的微缩,源极/漏极的接面变浅,源极/漏极的硅化层厚度也必须随之微缩而变薄,以避免小工程漏电界面,举例来说,对0.18μm线宽的技术,其接面深度已小于0.1μm,而其源极/漏极硅化层的厚度可能只有0.01~0.04μm。

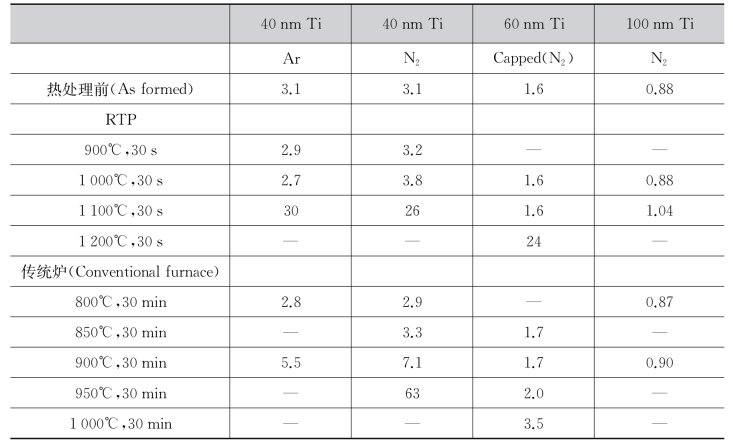

一般最常用的金属硅化层为硅化钛,其他如硅化钴,硅化镍等近年来也由不少专家学者在研究。硅化钛的形成,一般都采用量阶段退火方式。首先以溅射或化学气相淀积法生长一金属钛膜;或以共溅法溅射一钛硅层,接着在650℃左右,进行第一阶段退火,使金属钛与接触硅基板反应,形成硅化钛。此时的硅化钛主要是由电阻值较高的C49相构成。借助于溶液(如5∶1∶1的去离子水∶30%双氧水∶NH4OH)来去除淀积于绝缘层上未反应的金属钛。并顺便去除反应过程中,在表面形成的氮化硅层。接着在含氮或氩气体中,在800℃左右,进行第二阶段退火。第二阶段退火可将电阻值较高的C49相硅化钛转换成电阻值较低C54相的硅化钛,而达到最低的面电阻。如表7-6所示,金属硅化层的面电阻值取决于淀积金属厚度,退火后温度、时间及气体(氩或氮)。

表7-6 硅化钛面电阻工艺参数(金属钛厚,退火方式及温度时间)的关系

注:Sheet resistance of TiSi2layer after heat treatments from 800℃to 1200℃for 30 s or 30 min in N2or Ar ambient,Three silicide thicknesses were used(starting from 40,60 and 100 nm Ti).yielding a silicide layer of±50,90 and 150 nm,respectively,value are inΩ/sp.

传统高温灯管工艺不可避免的长热预算造成杂质扩散及接触面变深,严重影响晶体管特性,例如一些短沟道效应像穿透,临界电压降低等均恶化,使元件微缩困难。而对自行对准硅化处理工艺,传统的高温灯管退火方式极易造成源极/漏极及栅极间的短路。这是因为源极/漏极及栅极的硅化钛间仅由薄边壁空间隔离。更为主要的是,随着硅化钛变薄,其所需退火反应时间反而需要更长,而与短热预算的目的背道而驰。以上因素均显示对深亚微米元件必须借助RTP工艺。

当淀积金属层形成硅化层时,将有部分硅材料被消耗掉。如第5章表5-10所示,每淀积一单位金属钛,会消耗掉2.24单位厚度的硅材,而形成一2.5单位厚度的硅化钛。对硅化钴而言,每淀积一单位厚度的钴,会消耗掉3.63单位厚度的硅材,而形成一3.49单位厚度的硅化钴。

硅化钛虽然在所有硅材料中应用最广,然而当多晶硅栅极线宽微缩至0.5μm以下时,硅化钛无法在狭窄的栅极上,形成高导电性C54相,使栅极导电性恶化。硅化钴虽然没有类似效应,然而硅化钴不能还原氧化硅,所以事先适当的清洁工作就显得非常重要。如图7-46所示,要得到相同的面电阻,硅化钴需要消耗较厚的硅材,这也使的浅接面的形成比硅化钛更受限制。此外,一些掺杂物在硅化钴中扩散速度很快,因此对以P+型多晶硅为P型晶体管栅极的次0.25μm技术,CoSi2若直接连接P+和N+多晶硅时,可使得硼离子扩散至N型多晶硅,而磷离子则扩散至P型多晶硅,造成多晶硅特性的漂移。可以利用TiN/Poly的变层栅极来避免这一问题。

图7-46 硅化物形成时所需消耗硅材厚度对面电阻的关系

淀积于硅基板上的钴受到RTP处理时,其面电阻的变化情形参见第5章图5-93。在400℃左右,金属钴开始形成Co2Si及CoSi,使面电阻上升;在500℃全部转换成高电阻CoSi;在700℃以上时,随着高导电性CoSi2的形成,面电阻也降到最低。

6.磷硅玻璃(PSG)或硼磷硅玻璃(BPSG)的缓流及再缓流

PSG或BPSG多用于栅极与第一层金属间的绝缘层,故其表面起伏度对后段工艺的完整性有相当大的影响。BPSG开接触孔前面的缓流,或开接触孔后的再缓流,其特性取决于材料成分(注:含磷及含硼的百分比)、环流或再环流条件(温度、时间、气体等),以及事先的密质比的处理过程。一般而言,长时间、高温及水蒸气下,其缓流或再缓流的效果越好。而含硼的质量百分比每增加1%,所需的缓流温度约可降低40℃。然而含硼量需保持5%以下,以维持材料的稳定性。而用30秒的RTA处理,其缓流效果大概相当于用约低100到175℃的传统长时间灯管所得。如图7-47所示,事先的密质比处理也对缓流效果有很重要的影响;若没有经过700℃,20 s的密质比处理,则即使加以同样的1100℃,20sRTA缓流处理,仍不见显著效果。

7.垒晶生长

图7-47 密质处理对再缓流的影响

(a)不经密质处理(b)600度,20 s密质处理(c)700度,20 s密质处理

生长垒晶的RTP设备,其对氧化纯度的要求,比别的RTP工艺要严格很多。对温度的控制要求也很严,以求准确控制淀积率,并避免位错的产生。常用的生长气体有SiH4,SiH2Cl2,Si2H6;混以不同组合的H2,N2或HCl。以SiH4生长比以SiH2Cl2生长有较快的速率。而HCl加入SiH4中,可造成垒晶生长速率的骤减。[4]近年来有文献报道,用Si2H6可在较低的温度生长垒晶。而B2H6,GeH4等则常被用来掺杂硅垒晶,或是生长可用于高频的硅锗材料及元件。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。