前文已经述及,功率MOSFET和传统MOSFET的工作原理基本相同,但作为功率器件,其在结构设计、制造技术及特性方面与典型的MOSFET则完全不同。与GTR器件类似,功率MOSFET也是以晶体管原理为基础将微电子技术的发展成果应用到电力电子领域的功率器件。

传统的MOSFET结构把S极、G极、D极都安装在Si片的同一侧面上,因而MOS中的电流是横向流动的,电流容量不可能太大。要想获得大功率,必须有很高的沟道宽长比W/L,而L受制版和光刻工艺的限制不可能做得很小,因而只好增加管芯面积,这是不经济的甚至是难以实现的。因此,MOS器件开始始终停留在小功率范围内,难以步入大功率应用领域。

功率MOSFET要在保留和发挥MOS器件本身特点的基础上,着重于发展和提高功率特性,增大MOS器件的工作电流和电压,突破原有器件的极限。由垂直导电结构组成的场效应晶体管称为VMOSFET,V表示垂直(Vertical),VMOS在传统MOS基础上进行了下述3项重大改革:

1)垂直安装漏极实现垂直传导电流,将在MOS结构中与源极和栅极同时水平安装在硅片顶部的漏极改装在硅片的底部,充分利用硅片面积,为获得大电流容量提供了前提条件;

2)设置了高电阻率的N-型漂移区,不仅提高了器件的耐压容量,而且降低了结电容,并且使沟道长度稳定;

3)采用双重扩散技术代替光刻工艺控制沟道长度,可以实现精确的短沟道制作,降低了沟道电阻值,提高工作速度,并使输出特性具有良好的线性。

从功率MOSFET的发展过程看,典型的最基本结构主要有3类:LDMOS、VVMOS及目前应用最广泛的VDMOS。

1.VVMOSFET

VVMOS这里的第一个V表示垂直,第二个V表示V形槽(V-groove),它是早期进入到强电领域的高速器件。1975年,美国Siliconix公司将V形槽腐蚀技术移植到MOSFET上,成功地制造出纵向V形槽功率MOSFET,从而开创性将功率MOSFET推向强电领域。

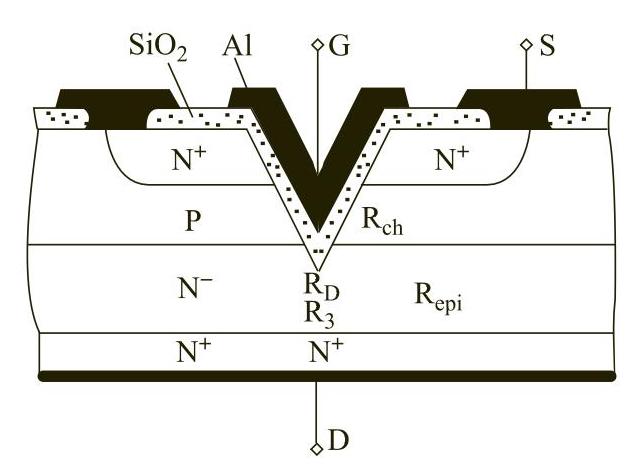

图3-3为VVMOS的结构图。它的制造工艺简述如下:在一块N+型高掺杂浓度的Si衬底上,通过外延生长形成N-漂移区,在N-高阻漂移区内有选择的扩散出P型沟道体区,再在P区内有选择的扩散N+源区,然后利用各向异性的腐蚀技术刻蚀出V形槽,槽底贯穿P区,最后在V形槽的侧壁处形成MOS系统。这里,N+和N-区共同组成漏区;源区、体区之间短路,源区PN结零偏;漏区PN结反偏,承担工作电压。

图3-3 VVMOS结构图

当栅极加以适当的电压时,表面电场效应就会在P型体区靠近V形槽壁的表面附近形成N型反型层,成为沟通源区和漏区的导电沟道。这样,电子从N+源区出发,经过沟道流到N-漂移区,然后垂直的流到漏极,首次改变了MOSFET电流沿表面水平方向流动的传统概念,实现了垂直导电。这一突破为解决大电流技术难题奠定了基础。

但是VVMOS存在如下的缺点:靠腐蚀形成V形槽,很难精确控制;V形槽易于受离子沾污造成阈值电压不稳定;V形槽底部为尖峰,电场较集中,难以提高击穿电压。针对第3个问题曾开发出U型槽的VUMOS,如图3-4所示。VUMOS在腐蚀时前沿未达到V形槽底部时就停止腐蚀,这样槽底是平的,可缓解电场集中的问题。但这种腐蚀亦很难控制。

(https://www.xing528.com)

(https://www.xing528.com)

图3-4 VUMOS结构图

20世纪80年代以来VVMOS已被VDMOS所代替,目前各国主要研究和发展的都是VDMOS。

2.VDMOSFET

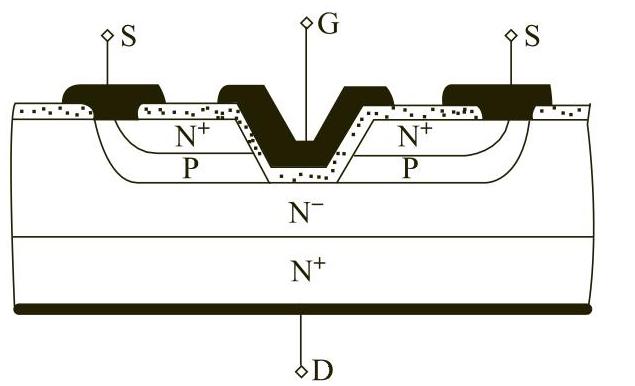

VDMOS指垂直导电双扩散MOS,这里的D表示扩散(Diffusion)。与VVMOS不同,它不是利用V形槽形成导电沟道,而是利用两次扩散形成的P型区和N+型区在硅片表面处的结深之差形成沟道。这是目前发展最快、使用最广的功率MOS。

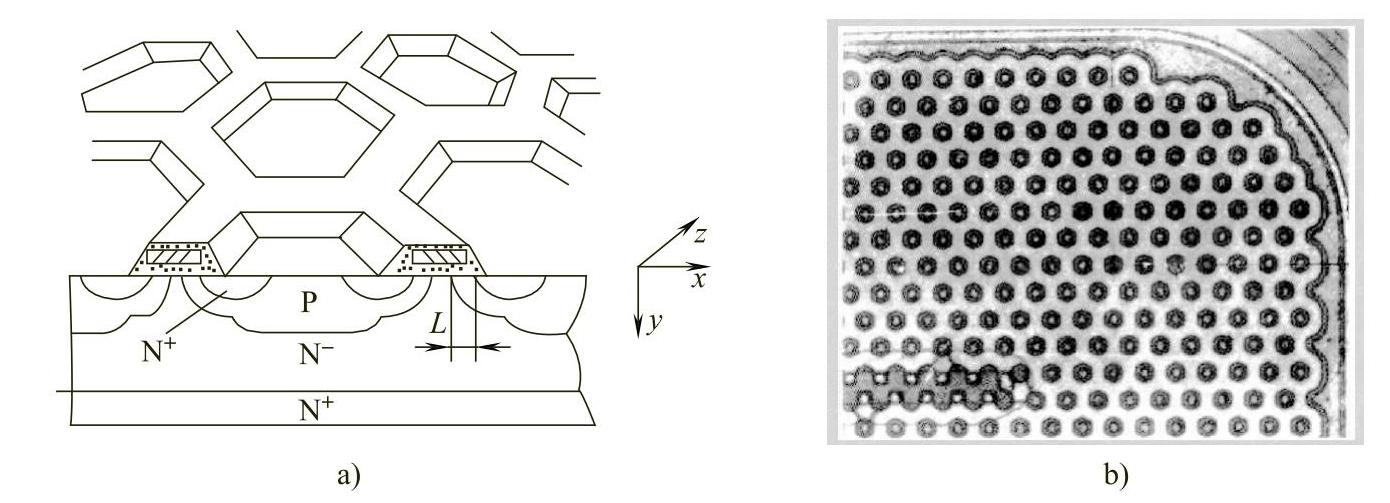

VDMOS的结构图如图3-5所示。电子在沟道内沿表面流动,然后垂直地被漏极接收。在高阻外延层N-上采用平面自对准双扩散工艺,利用硼磷两次扩散差,在水平方向形成短沟道(1~2μm),通常N+源区和浓硼P+区均由扩散形成,P阱区由离子注入形成。如图3-6所示,VDMOS采用多晶硅栅双层布线、多单元并联结构,改善了芯片的电流分布。多单元并联结构不仅使每个单元沟长缩短,且所有MOS单元的沟道是并联在一起的,因而沟道电阻大幅度减小,可提高通态电流;另一方面,沟长缩短,则载流子在沟道中的渡越时间缩短,且因为所有沟道并联,允许很多载流子同时渡越,可使器件开通时间极短,提高工作频率。多单元并联的单元密度可达1.86×104个/cm2,新一代MOS达1.12亿/in2,约22×104个/cm2。

图3-5 VDMOS结构图

图3-6 VDMOS的多单元并联结构

a)剖面图 b)俯面图

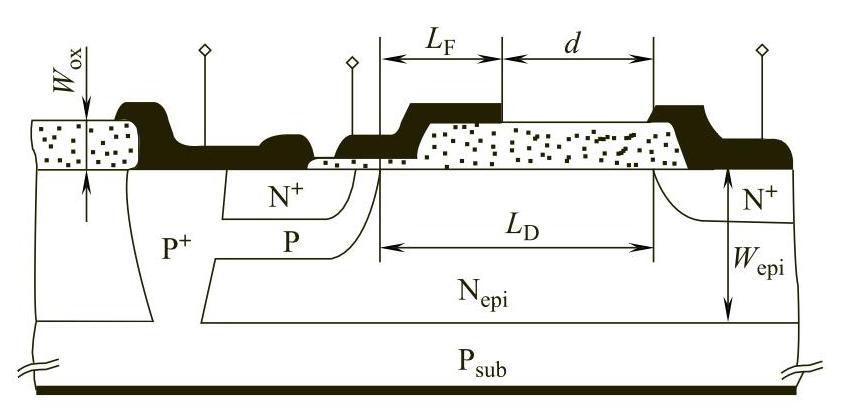

图3-7 LDMOSFET结构图

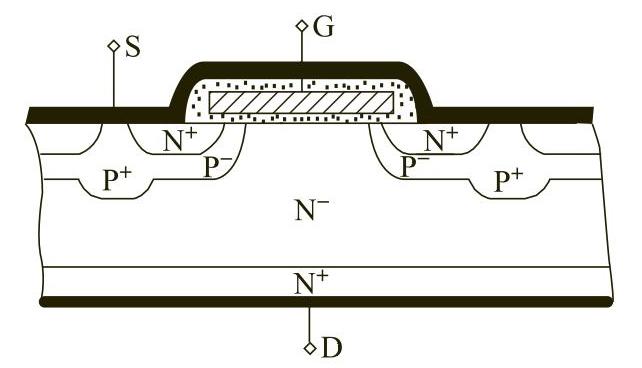

3.LDMOSFET

LDMOSFET指横向双扩散MOS,这里的L表示横向(Lateral)。LD-MOSFET利用硼磷两次扩散差精确控制沟长,它在普通MOS的沟道与漏区之间增加了一个轻掺杂的N-漂移区,其结构图如图3-7所示。LDMOSFET的源、漏、栅3个电极均分布在上表面,可以方便地与其他器件集成,所以在高压集成电路HVIC和功率集成电路PIC中已广泛应用。由于发生了面积竞争,一般电力集成器件中不采用此种结构。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。